# Journal of Materials Chemistry C

**View Article Online**

## PAPER

Cite this: J. Mater. Chem. C, 2022, 10, 3196

## Advanced artificial synaptic thin-film transistor based on doped potassium ions for neuromorphic computing *via* third-generation neural network<sup>†</sup>

Yixin Cao,‡<sup>a</sup> Tianshi Zhao, <sup>(b)</sup>‡<sup>a</sup> Chun Zhao, <sup>(b)</sup>\*<sup>ab</sup> Yina Liu, <sup>cd</sup> Pengfei Song,<sup>ab</sup> Hao Gao<sup>e</sup> and Ce Zhou Zhao<sup>ab</sup>

As the basic and essential unit of neuromorphic computing systems, artificial synaptic devices have great potential to accelerate high-performance parallel computation, artificial intelligence, and adaptive learning. Among the proposed artificial synaptic devices, the synaptic transistors are well considered to be one of the most suitable devices for simulating artificial intelligence. So far, synaptic transistors based on iontronic have been proposed and proved to demonstrate great potential in artificial intelligence applications. However, little research specifically focused on improving the device's ability to mimic synaptic behaviour. Here, we proposed the enhancement of synaptic properties of the solution-based thin-film transistors based on potassium ion conduction in the dielectric layer for the first time. Due to the formation of a gated electrical double-layer, the transistor exhibited an enlarged memory window. Based on this, the excitatory postsynaptic current in the synaptic thin-film transistor was modified accordingly, which further enhanced the suitability of the proposed synaptic thin-film transistor for simulating biological synapses. In addition, considerable synaptic properties were evaluated elaborately, including paired-pulse facilitation, short-term memory, long-term memory, and spike-time-dependentplasticity. Most importantly, according to the impressive results of the Artificial Neural Network algorithm's image recognition simulation, the simulation image recognition rate based on the mentioned artificial synaptic devices reached as high as 92%. Last but not least, in order to simulate biological neurobehavior more closely, the Spiking Neural Network algorithm was also successfully implemented to complete the specified machine learning task, which further proved the great potential of the synaptic devices in advanced low-power neural network systems.

Received 9th October 2021, Accepted 25th January 2022

DOI: 10.1039/d1tc04827a

rsc.li/materials-c

## Introduction

With the increase in the amount of data and demand for parallel computing, modern computers based on the von Neumann architecture are facing severe challenges of inefficient information processing.<sup>1–3</sup> Inspired by biological neural network systems, massively parallel neuromorphic computing was then proposed accordingly.<sup>2,4</sup> Unlike the traditional logic

circuit with transistors connected by only one or less than a handful of other components, one neuron in the neural network could connect to a thousand other neurons.<sup>2</sup> Since information processing can be highly parallel within a dense neural network, the data selection characteristics of neural networks are considered to be more power-efficient for artificial intelligence than the existing von Neumann computing architecture.5-8 The basic and essential unit in a neural network is the synapse, which is regarded as the functional connection between two adjacent neurons in the biological brain.<sup>9</sup> The strength of the synapse, *i.e.*, the synapse weight, could be adjusted and memorized, through which the neuron can transfer and analyze the information.<sup>7,9,10</sup> Therefore, the development of artificial synaptic devices towards an artificial neural network to mimic similar functions of the biological neural network is greatly worthy of investigation. Over the past decades, significant efforts have been extensively devoted to developing a synaptic device to trigger synaptic plasticity and non-volatility. In order to mimic and simulate synaptic activity,

<sup>&</sup>lt;sup>a</sup> Department of Electrical Engineering and Electronics, University of Liverpool, Liverpool L69 3GJ, UK. E-mail: Chun.Zhao@xjtlu.edu.cn

<sup>&</sup>lt;sup>b</sup> School of Advanced Technology, Xi'an Jiaotong-Liverpool University, Suzhou 215123, China

<sup>&</sup>lt;sup>c</sup> Department of Applied Mathematics, Xi'an Jiaotong-Liverpool University, Suzhou 215123, China

<sup>&</sup>lt;sup>d</sup> Department of Applied Mathematics, University of Liverpool, Liverpool L69 7ZD, UK

<sup>&</sup>lt;sup>e</sup> Eindhoven University of Technology, Eindhoven, The Netherland

<sup>†</sup> Electronic supplementary information (ESI) available. See DOI: 10.1039/d1tc04827a

$<sup>\</sup>ddagger$  These authors contributed equally to this work.

typically, the two-terminal memristors with reversible analogue switch behavior such as oxide-based resistance random access memory (RRAM),<sup>11,12</sup> ferroelectric memory,<sup>13,14</sup> and phasechange memory (PCM)<sup>15,16</sup> were well studied and reported. Nevertheless, it is considered to be a significant obstacle for them to enable both learning and signal transmission simultaneously.<sup>17</sup> In addition, the reduced control of conductance changes and asynchronous read/write operations limits the further application of two-terminal memristor devices as synaptic elements. Although several solution schemes based on consecutive update-verify procedures have been initiated and attempted to modify the weight adjusting procedure of synaptic devices,<sup>3</sup> they further induced energy-expensive and device-todevice access, and increased the complexity of peripheral circuit design from application perspectives. Consequently, the energy-saving advantages of neuromorphic computing in data processing will no longer hence exist.<sup>18-21</sup>

To overcome these mentioned challenges, synaptic transistors have been proposed accordingly, such as ferroelectric-gate synaptic transistors and electrolyte-gate synaptic transistors.9,14,22,23 Compared with two-terminal memristor devices, the synaptic transistor with individually controllable three terminals can effectively prevent crosstalk between adjacent devices, allowing selective and parallel weight update.<sup>24</sup> In addition, the channel conductance between the source (S) and the drain (D) electrodes of the synaptic transistor-like devices could be adjusted by the gate (G) voltage, which is recognized as synapse weight.<sup>10</sup> Therefore, neuromorphic computing is widely considered to be realized with a broad application prospect via three-terminal synaptic transistors. Recently, the mechanism for devices to possess synaptic properties has been proposed tentatively, such as electrostatic modulation, iontronic theory, and ferroelectric effect theory.<sup>2,14,25-28</sup> Moreover, many kinds of research are worth discussing on how to optimize the mechanism of synaptic devices. At the same time, it is worthwhile to study the mechanism of the synaptic transistors from the perspective of material characterization. In addition, diverse research of neuromorphic applications still relies on traditional algorithms that have a weight updating process different from the real biological neuron system, such as ANN. Therefore, simulating biological neural networks more realistically in neural networks is of significant worth studying.

Here we propose a novel technology of doping potassium  $(K^{+})$  ions in the dielectric layers to enhance the synaptic characteristics of solution-processed synaptic thin-film transistors (TFT) for the first time. For biological individuals, as an indispensable element in the human body, K<sup>+</sup> ions play an important role in nerve signal transmission.23 For a gated transistor-like device, the K<sup>+</sup> in ion conducted dielectric contributes to the formation of the electric double-layer (EDL) at the interface between the dielectric and semiconductor layer, which leads to an increase of the controllable and repeatable memory window.<sup>2</sup> As a result, the transmission characteristic curve of the synaptic transistor will be more adaptable to mimic the synaptic activity. In addition, due to the effects of electrostatic modulation and electrochemical doping, devices doped by K<sup>+</sup> ions have greater relaxation time, causing the artificial synaptic transistor similar to the real biological synapse. For the proposed synaptic transistor, the indium oxide  $(InO_x)$  and alumina (AlO<sub>r</sub>) were served as the n-type channel and dielectric materials, respectively. Both  $AlO_x$  and  $InO_x$  thin films were prepared by solution method, which is well proved to have low cost and high composition controllability.<sup>29</sup> The synaptic plasticity was then simulated, such as paired-pulse facilitation (PPF), short-term memory (STM), long-term memory (LTM), spike-time-dependent-plasticity (STDP). Furthermore, the image recognition process was simulated using Artificial Neural Network (ANN) and Spiking Neural Network (SNN) algorithms. The simulated image recognition rate by ANN algorithms after 20 learning epochs reached 92%, which is close to the theoretical value that the learning rate is 1 (96%). In addition, although ANN's deep learning model has proven its powerful learning capabilities, it requires expensive computing resources and significant power consumption, making it difficult to be applied on the mobile edge devices such as smartphones and watches.<sup>30</sup> Furthermore, ANN employs a "classical" backward propagation approach in order to demonstrate classification. The backward propagation has no relation with neuromorphic computing as it only utilizes the static weight of the synapses  $(G^+ - G^-)$  but not their complex temporal properties. Therefore, the SNN algorithm, another advanced neuromorphic calculation model for the 3rd generation neural network with significant energy efficiency, has been proposed. Being an artificial neural network constructed using knowledge observed in biology, SNN uses spatiotemporal information (such as STDP) to update synaptic weights based on local learning rules,<sup>31</sup> in which neurons connect neurons through synapses with adjustable weight values. Moreover, some recent study suggests that the STDP learning rule is involved in the formation of associative memory.<sup>32</sup> Therefore, SNN is capable of more closely mimicking the working mode of biological synapses. In this work, the Mixed National Institute of Standards and Technology (MNIST) data set was also successfully identified under the SNN algorithm and well proved to obtain extremely low energy consumption.

### **Experimental section**

For the solution preparation, the AlO<sub>x</sub> precursor solution with a concentration of 2.5 M was prepared by dissolving aluminium nitrate nonahydrate (Al(NO<sub>3</sub>)<sub>3</sub>·9H<sub>2</sub>O, Aladdin) in deionized water (DI water). Based on the K<sup>+</sup> doping concentration, the 0, 1, and 10 at% K<sup>+</sup> ion-doped AlO<sub>x</sub> precursors were prepared by adding 0, 0.025, and 0.25 M potassium chloride (KCl, 99.99% metals basis, Aladdin) into the AlO<sub>x</sub> precursor solution, respectively. The InO<sub>x</sub> precursor solution with a concentration of 0.15 M was prepared by dissolving indium nitrate hydrate (In(NO<sub>3</sub>)<sub>3</sub>·xH<sub>2</sub>O, Aladdin) in deionized water (DI water). Subsequently, the prepared precursor solutions were ultra-sonicated and filtered through a 0.45 µm poly (ether sulfone) (PES) syringe to obtain transparent solutions.

For TFTs fabrication, the heavily doped n-type silicon  $(n^{\ast\ast}\,Si)$  was utilized as the gate substrate. In order to prepare the

dielectric layer, the AlO<sub>x</sub> precursor solution with and without specific K<sup>+</sup> ion doping were spun onto the plasma-treated n<sup>++</sup> Si substrate and then annealed at 300 °C under ambient atmosphere for 30 minutes. After that, the InO<sub>x</sub> precursor solution was spun onto the surface of the dielectric layer and then annealed at 250 °C for 30 minutes in an ambient atmosphere. Finally, the Al source and drain electrodes were deposited onto the semiconductor layer through thermal evaporation. The channel length (*L*) and width (*W*) were 10 and 150 µm, respectively, with a thickness of 100 nm.

The surface roughness of the  $K^+$  doped AlO<sub>x</sub> layers was observed by atomic force microscopy (AFM, Bruker Nanoscope V). The surface morphology of the AlO<sub>x</sub> layers was characterized by using a scanning electron microscope (SEM, Hitachi S4700). The element distribution of the sample was characterized by using the energy-dispersive X-ray spectroscopy (EDS, Hitachi S4700). The chemical bonds were measured through X-ray Photoemission Spectroscopy (XPS, Thermo scientific ESCALAB 250Xi with Al Ka X-ray source). The electrical characteristics and synaptic characteristics test of the TFTs were revealed utilizing a semiconductor analyzer (Keysight, B1500 A) in the dark condition at room temperature.

### **Results and discussion**

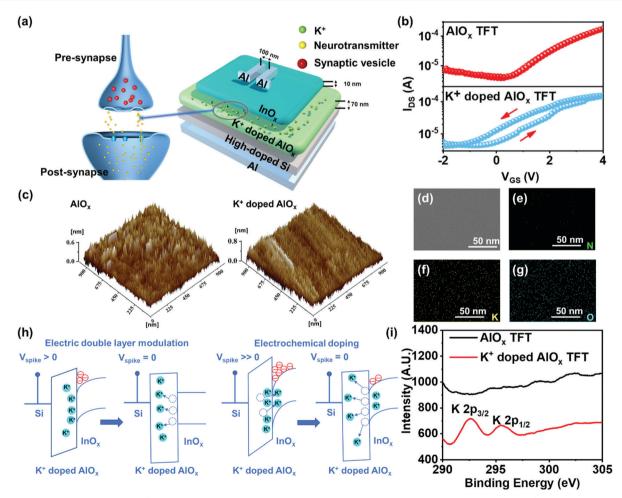

Generally, as depicted in Fig. 1a, for biological individuals, signals are transmitted from presynaptic neuron to postsynaptic neuron through synapses in nervous systems.<sup>33</sup> When presynaptic neurons receive external stimuli, ions in the extracellular fluid enter synaptic neurons through ion conduction and form memory by generating graded potentials and action potentials.<sup>34</sup> In order to mimic the behaviour of biological synapses, the electrochemical artificial synaptic TFTs based on  $K^+$  doped AlO<sub>x</sub> dielectric and InO<sub>x</sub> semiconductor were fabricated as described in Fig. 1a. For these devices, the Al gate electrode, InO<sub>x</sub> semiconductor, and K<sup>+</sup> ions represent the presynaptic neuron, the postsynaptic neuron, and neurotransmitter, respectively. Fig. 1b shows the transfer characteristic curves of the TFTs with or without K<sup>+</sup> ions doped AlO<sub>x</sub> dielectric layer, indicating typical characteristics of n-type TFTs. According to the results, under the gate voltage  $(V_G)$  swept forward and backwards from -2 to 4 V, the devices with K<sup>+</sup> doped AlO<sub>x</sub> dielectric exhibit an obvious counter-clockwise hysteresis window than the ones without K<sup>+</sup> doping. This could be utilized as

**Fig. 1** (a) Schematic diagram of the K<sup>+</sup> doped AlO<sub>x</sub> synaptic TFT. (b) Transmission characteristics of AlO<sub>x</sub> with and without K<sup>+</sup> doped. (c) AFM images of AlO<sub>x</sub> with and without K<sup>+</sup> doped. (d) SEM image of surface topography in AlO<sub>x</sub> surface view. The EDS mapping of (e) N, (f) K, (g) O elements in AlO<sub>x</sub> coating on Si substrate. (h) K<sup>+</sup> ions migration in the K<sup>+</sup> doped AlO<sub>x</sub> solid-state electron by bias spikes. (i) XPS image of the surface InO<sub>x</sub> film.

the basis for the synaptic properties of the devices. In addition, from the distribution diagram in Fig. S1 (ESI<sup>†</sup>), it could be concluded that the device memory window in this work shows the normal distribution. In order to further investigate the surface morphology of the thin films, the AFM measurement was then operated, and the result is shown in Fig. 1c. The rootmean-square (RMS) roughness value of the AlO<sub>x</sub> film without K<sup>+</sup> ions is 0.138 nm, while the  $AlO_r$  film doped by K<sup>+</sup> ions is 0.202 nm. This phenomenon shows that doping did not deteriorate the surface roughness of AlO<sub>x</sub>, and all the deposited films are of nanoscale smoothness which is beneficial for fabricating a high-quality channel layer and advantageous for obtaining TFT with high stability.<sup>35,36</sup> The SEM image in Fig. 1d also indicates that the produced  $K^+$  doped AlO<sub>x</sub> film exhibits flat and dense properties. The element map scanning during the EDS analysis was operated accordingly, and the results are shown in Fig. 1e to Fig. 1g. It is worth noting that Fig. 1f demonstrates that the doped K<sup>+</sup> ions are evenly distributed in the film.

In the biological neuron network, information transmission is mainly in the form of a bioelectrical pulse. The nerve fibres of each neuron are not directly connected but separated by other substances. When a bias input reaches the end of presynaptic neurons, basic ion neurotransmitters are released into synapses, resulting in new electrical bias spikes on adjacent postsynaptic neurons.<sup>36</sup> Similarly, for artificial synaptic TFT, the mobile  $K^+$  ions in the AlO<sub>x</sub> dielectric act as neurotransmitters, resulting in the changing of the channel conductance. The mechanism of channel conduction modulation is proposed in Fig. 1h. When the positive electric spike is applied to the gate of the synaptic TFT, the moving  $K^+$  ions will drift toward the dielectric/semiconductor interface.<sup>37</sup> These migrated K<sup>+</sup> ions could modulate the channel conductance through two types of iontronic modulation processes: EDL modulation (under weak bias peak) and electrochemical doping (under strong bias voltage).<sup>25,37</sup> For EDL modulation, the migrated K<sup>+</sup> ions will accumulate at the dielectric/semiconductor interface, inducing the accumulation of channel electrons.<sup>38,39</sup> Consequently, the channel conductance will increase. Once the external electric field is removed, K<sup>+</sup> ions will diffuse back to their original equivalent position due to the concentration gradient within a short period of time, and the EDL will then disappear. For electrochemical doping, other than the EDL modulation, part of the migrated  $K^+$ ions will penetrate the  $InO_x$  channel, causing the increase of the channel conductance.<sup>40</sup> After the removal of the gate voltage, the penetrated K<sup>+</sup> ions will gradually diffuse back to the original equivalent position, and this process will take a long period of time, leading to long-term retention of the increased channel conductance.  $^{25\mathchar`-27}$  As mentioned above, the mobile  $K^{\!\!+}$  ions within K<sup>+</sup> doped AlO<sub>x</sub> dielectric contribute to the formation of an EDL and electrochemical doping, resulting in short-term retention and longterm retention, respectively.<sup>23,41-43</sup> To prove the existence of the EDL, the metal-insulated semiconductor structure device was fabricated (Fig. S2, ESI<sup>+</sup>). Moreover, the capacitance-voltage (C-V) and capacitance-frequency (C-F) were tested. Fig. S3a (ESI<sup> $\dagger$ </sup>) shows the C-V test result, in which the gate voltage increases from -2 to 4 V

and the capacitance of the device increases from 1.6  $\times$  10<sup>-7</sup> to  $5.3 \times 10^{-7}$  F cm<sup>-2</sup>. During the artificial synaptic TFT operation, these specific capacitances are maintained at a high level. Compared with the control group without  $K^+$  doping, the capacitance increased significantly, considering K<sup>+</sup> and protons in K<sup>+</sup> doped  $AlO_r$  strongly accumulate on the  $InO_r/K^+$  doped  $AlO_r$  interface to form EDL under the action of an electric field, which can be regarded as a nanogap capacitor with ultra-high capacitance, thereby increasing the capacitance.<sup>38</sup> Fig. S3b (ESI<sup>+</sup>) illustrates the C-F test result. The specific capacitance distribution can be divided into two areas, the high-frequency area with a small capacitance value (>10 kHz) and the low-frequency area with a large capacitance value (<10 kHz)). The one in the high-frequency region (>10 kHz) refers to a bulk electrolyte capacitance with a fastcharging speed. The increase in capacitance in the low-frequency region (<10 kHz) is reasonably related to the formation of an EDL at the  $InO_x/K^+$  doped  $AlO_x$  interface. The EDL obtains large capacitance through the migration and accumulation of ions on the interface.<sup>25,37</sup> Furthermore, the C-V relationship at several frequencies was tested, and the results are shown in Fig. S3c (ESI†). At 10 kHz–1 MHz, the capacitance exhibits a weak  $V_{\rm gs}$  dependence. At 1 kHz, with the increase of  $V_{\rm gs}$ , the capacitance increases significantly, indicating the presence of pseudocapacitance. Through the integration of the C-V curve, the total accumulated charge  $Q_{\rm T}$  can be found:43

$$Q_{\rm T} = \int C dV_{\rm gs} = Q_{\rm M} + Q_{\rm F}$$

where  $Q_{\rm M}$  is the mobile charge and  $Q_{\rm F}$  is the faradaic charge. The result is shown in Fig. S3d (ESI<sup>†</sup>). The total charge generated by the C-V integration at 10 kHz-1 MHz is almost the same, indicating that the interface charge has electrostatic properties. The  $Q_{\rm F}$  can be ignored at these frequencies, and the total charge is equal to the mobile charge. At the frequency of 1 kHz, the  $Q_{\rm T}$  in the devices showed the largest value. This could also be mainly attributed to the formation of interface EDL.43 To demonstrate the existence of electrochemical doping, X-ray photoelectron spectroscopy (XPS) scanning was performed on the surface of the InO<sub>x</sub> layer before and after a long-time strong gate bias (1000 s, 4 V) had been applied to the TFTs with or without K<sup>+</sup> doping. In order to make the comparison more obvious and explicit, 10%  $K^+$  doped AlO<sub>r</sub> was used for the experiment. According to the results in Fig. 1i, through the application of gate bias, the peaks of K 2p (292.6 eV) could be found in the InO<sub>x</sub> layer of the devices with  $K^+$  doping while could not for the ones without  $K^+$ doping.<sup>44</sup> However, since both the  $K^+$  doped AlO<sub>x</sub> layer and the  $InO_x$  layer were prepared by the aqueous solution method, during the  $InO_x$  fabrication, the precursor solution might dissolve part of the  $K^+$  from the  $K^+$  doped AlO<sub>x</sub> dielectric. Therefore, for  $K^+$  doped AlO<sub>x</sub> TFT without bias application,  $K^+$ ions could also be found on the  $InO_x$  surface (Fig. S4, ESI<sup>+</sup>). Nevertheless, according to the ratio of the peak intensities of K  $2p_{3/2}$  and In  $3d_{5/2}$  in the XPS spectra before (29.89%) and after (35.13%) the gate bias, it could be concluded that the content of K<sup>+</sup> ions in the InO<sub>r</sub> layer induced by electrochemical doping increases after the bias voltage (Table. S1, ESI<sup>+</sup>).

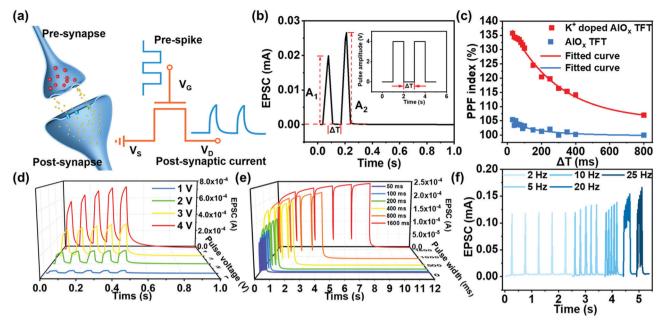

**Fig. 2** (a) The principle of signal transmission from pre-synaptic to post-synaptic in biological synapses and simulation of the electrical impulse of artificial synaptic TFT. (b) Two consecutive presynaptic spikes (4 V, 30 ms) generate EPSC. Interval time ( $\Delta t$ ) is 100 ms. (c) The PPF index is defined as the function of the ratio of A<sub>2</sub>/A<sub>1</sub> and two pulses (4 V, 30 ms) interspike interval ( $V_{ds} = 4$  V). (d) EPSC is generated by five presynaptic spikes (1 V to 4 V, 50 ms),  $\Delta t$  is 50 ms ( $V_{ds} = 2$  V). (e) The enhancement effect of five consecutive presynaptic pulses (2 V) on EPSC, the pulse time varies from 50 ms to 1600 ms ( $V_{ds} = 2$  V). (f) EPSC ( $V_{ds} = 4$  V) is generated by five presynaptic spikes (4 V, 30 ms) with different pulse frequencies (2 Hz–25 Hz).

In synaptic TFT, the excitatory postsynaptic current (EPSC) is used to manifest the channel conductance and indicate the response to presynaptic signals, *i.e.*, the gate bias (Fig. 2a).<sup>45</sup> When the gate bias is applied in the form of pulses, the EPSC in the synaptic TFT could show a modulated trend that effectively mimics the excitability changes in biological neurons (synaptic plasticity). As shown in Fig. S5 (ESI<sup>†</sup>), a positive gate pulse could cause an immediate increase of EPSC followed by a gradual recovery, while a negative gate pulse leads to an opposite response. Most importantly, the EPSC can be arbitrarily regulated, which is the research basis of synaptic devices.42,46,47 In the neuromorphological system, neurofacilitation, also named paired-pulse facilitation (PPF), is known as typical synaptic behaviour.48 Due to the memory effect, if two presynaptic peaks are close enough, the EPSC peak resulting from the first presynaptic peak cannot be eliminated entirely, and the peak generated by the second presynaptic peak will be enhanced accordingly.<sup>48,49</sup> A pair of presynaptic spikes (4 V, 30 ms) with a pulse interval ( $\Delta t$ ) of 20 ms was continuously applied to the gate, as shown in Fig. 2b. The second EPSC peak triggered by presynaptic pulses is much higher than that of the first. Fig. 2c depicts the PPF index as a function of the interval time between pairs of pulses. The PPF index curve can be fitted as follows double-phase exponential function:<sup>50</sup>

PPF index =

$$A_2/A_1 = 1 + C_1 \exp(-\Delta t/\tau_1) + C_2 \exp(-\Delta t/\tau_2)$$

where  $A_1$  and  $A_2$  are the first and second EPSC peaks,  $C_1$  and  $C_2$  are the initial facilitation magnitudes, and  $\tau_1$  and  $\tau_2$  are relaxation time constants. The curve shows that PPF decreases with the increase of  $\Delta t$ . For the case of AlO<sub>x</sub> TFT, the relaxation

times,  $\tau_1$  and  $\tau_2$ , are estimated to be 76.1 ms and 93.1 ms, respectively. For the case of  $K^+$  doped AlO<sub>x</sub> TFT,  $\tau_1$  and  $\tau_2$  are estimated to be 136.2 ms and 166.5 ms, respectively, which is similar to the relaxation time of synapses in organisms. The higher value of time constants shows that K<sup>+</sup> doping is indeed more suitable for simulating biological synapses with longterm memory characteristics.<sup>43,51</sup> For K<sup>+</sup> doped TFTs, the EPSC levels of five consecutive presynaptic spikes at different voltage levels with  $\Delta t$  of 50 ms are shown in Fig. 2d. With the increase of presynaptic voltage from 1 V to 4 V, the amplitude changing of EPSCs was also increased. The peak value of the postsynaptic current was affected not only by the magnitude of voltage stimulation but also by the pulses' width. When the width of the voltage pulse (4 V) increased from 50 ms to 1600 ms, the EPSC peaks of the TFT have more than doubled, as shown in Fig. 2e. Fig. 2f shows the EPSC levels of five presynaptic spikes (4 V) at different frequencies (2 Hz-25 Hz). It could be obtained that a higher frequency signal means a shorter interval between each peak, and a shorter interval time leads to a promotion of the EPSC. The ratio between the EPSC generated by the 5th peak and the 1st peak is defined as the current gain  $(A_5/A_1)$ . As expected, the current gain enhanced with the pulse frequency. When the pulse frequency is 25 Hz, the current gain reached 1.35, which is increased by 32% compared to the test result under 2 Hz. Therefore, synaptic TFT can be used as highfrequency filters for large-scale neural morphological computing systems with frequency or time coding.<sup>5,52</sup> These results indicate that the proposed synaptic TFT has synaptic plasticity for various presynaptic voltage spikes, just like the characteristics of biological nerves. The stronger the stimulus applied,

the stronger the response behaved.<sup>49,53</sup> In contrast, under the same pulses test for the TFTs without K<sup>+</sup> doping, the EPSCs quickly returned to the initial states after the removal of the pulses without an obvious rising trend (Fig. S6, ESI<sup>+</sup>). These results are well consistent with the above analysis and confirm the effectiveness of  $K^+$  ion doping. In addition, the synaptic behaviours of devices with 10%  $K^+$  doped AlO<sub>x</sub> TFT were also measured (Fig. S7, ESI $\dagger$ ). The excessive K<sup>+</sup> ion doping caused an intensive increase of the EPSC peaks to observe an upward trend with good linear characteristics. This means that this type of device is not suitable for further application in the machine learning field, which will be introduced in detail in the latter part. In addition, for artificial synaptic devices, lower energy consumption values are more conducive for the realization of large-scale calculations and more realistic simulation of biological synapses. As shown in Fig. S8a (ESI<sup>+</sup>), the EPSC response can still be triggered under extremely low  $V_{\rm ds}$  and electrical impulse stimulation, and its energy consumption can be calculated by the formula:54

#### $E = V_{\rm ds} \times I_{\rm ds} \times t$

where  $V_{ds}$  is the voltage applied to the drain terminal of the synaptic transistor,  $I_{ds}$  is the current flowing from drain to source terminal, and t is the width of the electrical pulse. The result is shown in Fig. S8a (ESI†). The energy consumption of our synaptic device is 2.5 fJ. The comparison of artificial synaptic energy consumption between K<sup>+</sup> doped AlO<sub>x</sub> artificial synapse TFT and other recently published work are shown in Fig. S8b (ESI†), which indicates a lower energy consumption of

this work, similar to a biological system (10 fJ per synaptic event).<sup>55–65</sup> This result indicated that the device in this work has great potential in simulating the behaviours and energy consumption of human brain synapses."

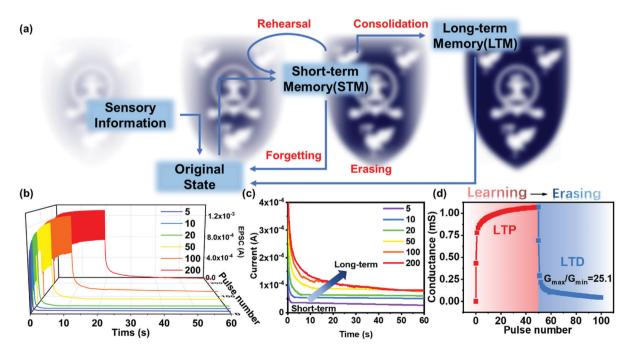

The multi-storage model proposed by Atkinson and Shiffrin (as demonstrated in Fig. 3a) shows that human memory has three components: sensory memory, STM, and LTM.<sup>66</sup> The external environment input of new information is firstly stored in the sensory register as a sensor memory in a short period and then selectively converted to temporary STM in short-term memory storage or permanent LTM in long-term memory storage. If the sensory stimuli are repeated frequently, STM will be transformed into LTM. Due to the complexity of the neural processes known to be realized in neural engineering, it is difficult to prove that neural processes are interconnected. However, the TFTs can simulate the synaptic function of STM and LTM characteristics by using input repetitive pulse stimulation. As shown in Fig. 3b, a series of electrical pulses (number of 5, 10, 20, 50, 100, 200) with a fixed duration of 100 ms and a voltage intensity of 4 V was applied to the synaptic device. It shows that EPSC rises under a positive pulse, which can be regarded as "learning". The learning state is defined as the state at the end of the positive pulse. When presynaptic spikes had finished, the synaptic weight decays spontaneously over time. This decay process is similar to the forgetting process of biological synapse behaviour. In Fig. 3c, with the increase of the number of learning pulses, the drop of EPSC as a function of time gradually slows down, indicating the transition from STM to LTM.3,49 In addition, due to the presence of electrochemical

Fig. 3 (a) The multi-storage model of human memory was proposed by Atkinson and Shiffrin. (b) EPSC is generated by different numbers (5–200 times) of presynaptic spikes (4 V, 80 ms), and EPSC is observed to be gradually increased. (c) As the number of applied pulses increases, it changes from STM to LTM. After different numbers (5–200 times) of presynaptic spikes stimulate 60 s, the current is still stored. (d) Conductance change during learning (by positive spike: 4 V, 100 ms) and erasing (by negative spikes: 2 V, 100 ms).

doping, the charge can be preserved for a long time. Furthermore, the learning process based on positive pulses is reversible, which means that the negative pulse input could accelerate the EPSC decrease process. Based on this, in addition to long-term potentiation (LTP), the device also exhibited long-term depression (LTD) characteristics. The LTP and LTD together formed the basis of neural computing. As shown in Fig. 3d, 50 positive voltage pulses were applied to enhance the synaptic weight (channel conductance, G) and simulate the "learning" function. Then 50 negative voltage pulses were applied to depress the synaptic weight and represent the "erasing" function.

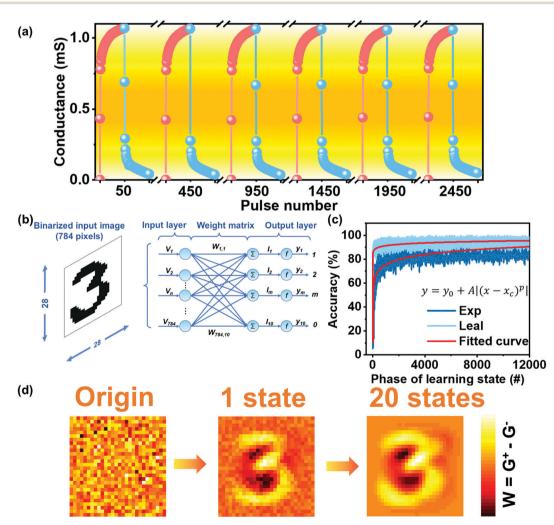

In order to investigate the stability of the device, 25 mentioned full-scale "writing" and "erasing" cycles were tested in the device, as shown in Fig. 4a. The results show that the device's synaptic behaviour remains stable after 2500 pulses. Ideally, the linear proportions existed between the increase and decrease of G and the number of electrical pulses. In fact, the cumulative conductance is unable to exactly follow a simple linear correlation, which leads to non-linearity (NL) of the synaptic weight update. The value of G could be then described by function:<sup>3</sup>

$$G_{\rm P} = B_{\rm P} [1 - \exp(\gamma P/A_{\rm P})] + G_{\rm min}$$

$$G_{\rm D} = -B_{\rm P} [1 - \exp(P - \gamma/A_{\rm D})] + G_{\rm max}$$

$$B_{\rm P/D} = (G_{\rm max} - G_{\rm min})/[1 - \exp(-\gamma/A_{\rm P/D})]$$

$G_{\rm P}$  and  $G_{\rm D}$  are the fitted conductance of "writing" and "erasing" processes in Fig. 3d. *P* is the normalized pulse number,  $\gamma$  in this work is 1, and *A* is a parameter that can control the nonlinear relationship between conductance and the number of pulses and is inversely proportional to the value of NL (Table. S2, ESI†).<sup>3</sup> According to the results, the weight-renewed NL has a relatively low gain for the potentiation mode in the "learning" process (NL<sub>P</sub> = 0.8884), while the value of the "erasing" process (NL<sub>D</sub> = 3.54) is asymmetrically high. This corresponds to previous studies that the positive and negative pulses of the same amplitude cause the EPSC to rise and fall in different amplitudes.<sup>67</sup>

Fig. 4 (a) Use 25-cycle pulses (50 positives (4 V) and 50 negatives (-2 V) pulses with a pulse duration of 50 ms and an interval of 50 ms) to simulate the synaptic TFT channel conductance. (b) ANN structure used in the simulation. (c) Simulation of MNIST digit recognition accuracy based on synaptic TFT perceptron neural network. (d) Mapping images of test data sets for three different learning epochs.

To further explore the neuromorphic computational simulation capabilities of  $K^+$  doped AlO<sub>x</sub> TFT synaptic devices, a handwritten artificial neural network was developed, which can simulate the numbers in the revised MNIST data set through the ANN algorithm.<sup>3,68</sup> Specifically, as shown in Fig. 4b, since the synapse layer is composed of  $28 \times 28$  input neurons, the input pattern contains the same number of pixels, which are fully connected with 7840 synaptic weights and converted into 10 output neurons. It is worth noting that the synaptic TFTs have only positive channel conductance, while there are positive conductance and negative conductance in the weight matrix. Therefore, the conductance difference between two equivalents synaptic structures was defined as the synapse weight, which can be expressed as  $W = G^+ - G^-$ . Here, the symbol W represents the synapse weight. Based on the backpropagation algorithm, W increases as  $G^+$  increases and decreases as  $G^-$  increases. As described in Fig. 3d, the G of the device can be increased by applying a positive voltage pulse, and the application of a negative pulse will cause the G of the device to decrease. The conductance change extracted from the "learning" and "erasing" curves describes the detailed information of the synaptic weight change. It can be concluded that the  $G_{\text{max}}/G_{\text{min}}$  ratio of the synaptic device is 25.1. According to previous literature, good linearity and a high  $G_{\text{max}}/G_{\text{min}}$  ratio will improve the final recognition accuracy.<sup>67,69</sup> In the simulation, due to the high  $G_{\text{max}}/G_{\text{min}}$  ratio (25.1) and suitable linearity ( $NL_P = 0.8884$ ,  $NL_D = 3.54$ ), the recognition accuracy can reach 92% after 20 learning cycles, as shown in Fig. 4c.

Moreover, the experimental device's recognition accuracy also approaches the ideal accuracy based on linear weight updating route and unlimited  $G_{\text{max}}/G_{\text{min}}$  (96% after 20 periods). As shown in Fig. 4d, considering the handwritten number "3" as an example, the output matrix was drawn in the mapped image (28 × 28 pixels). Initially, the output was random without any image information, and after 20 learning states, the shape of "3" became recognizable accordingly.

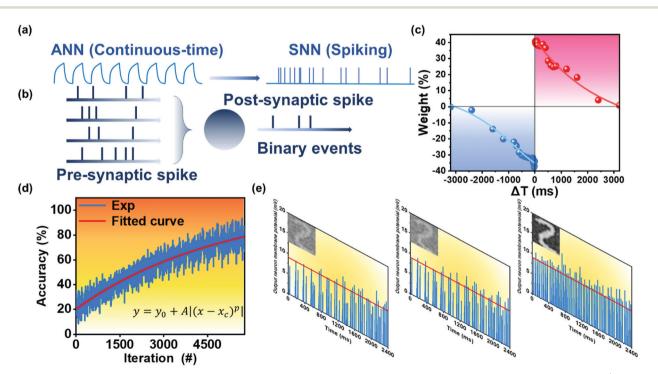

In addition, the SNN algorithm-based simulation for image recognition was further attempted. Compared with ANN, SNN is closer to the actual working model of biological synapses. As shown in Fig. 5a, the ANN algorithm is based on a continuous mathematically-defined nonlinear activation function. However, the information processing modes of the human brain and the artificial neural networks are distinguished from each other. Typically, the information is encoded as binary spikes in the human brain, while most artificial neural networks use realvalued vectors to represent data. As a comparison to ANN and shown in Fig. 5a, the SNN is all-or-none output in response to input spikes. It is also regarded as the "third-generation" neural network since it has the potential to replace deep learning methods in the fields of computational neuroscience and biological trusted machine learning.<sup>70</sup> The binary (spike or no spike) operation is considered to be more suitable for fast and energy-efficient simulation on hardware devices.<sup>71</sup> In addition, the SNN can emulate the human brain more faithfully on artificial neuromorphic hardware due to its noise resiliency, energy efficiency, and convenient implementation.<sup>72</sup> The

**Fig. 5** (a) ANN algorithm and SNN algorithm function diagram. (b) SNN algorithm weight update diagram. (c) STDP response based on  $K^+$  doped AlO<sub>x</sub> synaptic devices. (d) Image recognition rate of SNN algorithm. (e) Different stage results of training the SNN using the MNIST data set. *Via* the generation characteristics of the SNN, the image is reconstructed using the training weights connected to each output neuron to view the learning situation of the network.

shaping of weight is based on the following two rules: Firstly, any synapses that contribute to the firing of postsynaptic neurons should become stronger, and their value should increase; Secondly, the synapse that does not contribute to the firing of the postsynaptic neuron should be weakened. Typically, as shown in Fig. 5b, multiple neurons are connected to a single neuron through synapses. Each presynaptic neuron fires at its own rate, and the spike is sent forward by the corresponding synapse. The strength of the spikes converted to postsynaptic neurons depends on the strength of the connecting synapses. Due to the input spike, the membrane potential of the postsynaptic neuron increases and emits a spike after crossing the threshold. When the postsynaptic neuron spikes, it will monitor which presynaptic neurons help it fire. This can be acquired by observing which presynaptic neurons spiked before the postsynaptic neurons spiked. Therefore, the postsynaptic spike is then induced by increasing the membrane potential, so the corresponding synapse is strengthened accordingly.

In order to operate the SNN simulator, the STDP behaviour of the device served as the principle rule to update the weights and classify patterns, which is considered to be a biological process used by the brain to modify its neural connections. Fig. 5c shows the STDP curve of the synaptic device under electric pulse  $V_{\rm ds}$  of 1 V and  $V_{\rm gs}$  of 1 V with both pulse duration of 30 ms. The STDP is the change in the synaptic weight ( $\Delta w$ ) between pre-and postsynaptic spikes which can be modulated by using relative time duration between them.<sup>73</sup> The  $\Delta w$  is defined as  $(G_{\rm Post} - G_{\rm Pre})/G_{\rm Pre}$ , where  $G_{\rm Pre}$  and  $G_{\rm Post}$  are conductance after the pre-and postsynaptic spikes, respectively. It could be observed that if the pre-spiking precedes the postspiking ( $\Delta t > 0$ ), the connection strength of the synapse between two neurons would be reinforced. On the contrary,  $\Delta t < 0$  led to a depression phenomenon.

During the SNN simulation, the  $G_{Post}$  weight used is the conductance of 1 s after  $V_{\text{post}}$  or  $V_{\text{pre}}$ , and the maximum time interval  $\Delta t$  between  $V_{\text{post}}$  and  $V_{\text{pre}}$  is 3.2 s during the process of testing STDP. To prove this simulation further closer to the actual hardware conditions, a time interval as an additional inference period was added. Therefore, the 4.3 s, which is slightly larger than the summation of  $\Delta t$  and one-second postpone, was chosen as an additional inference period. Fig. 5d shows the simulation result of image recognition using the SNN algorithm. The recognition rate of the MNIST data set after training reached 86%. Fig. 5e shows the weights of all synapses connected to a specific output neuron (the number is 400) after training based on the MNIST dataset. The red line in the figure represents the variable threshold. The threshold of each mode was calculated based on the number of contained activations. As shown in the inset diagram, the trained weight matrix could successfully recognize the image.

## Conclusions

In summary, the solution-processed synaptic TFTs with  $K^+$  doping were fabricated and investigated. By doped  $K^+$  ions, the pristine  $InO_x/AIO_x$  TFTs exhibited enhanced synaptic behaviour. Based on

the strong interfacial electric-double-layer coupling effect and electrochemical doping effect, the K<sup>+</sup> doped transistors showed an obvious anti-clockwise memory window, which leads to a regulated EPSC behaviour. Moreover, several essential synaptic properties were measured, including PPF, STM, LTM, and STDP. Most importantly, under the simulation based on the ANN algorithm, the image recognition rate of the MNIST database for the proposed K<sup>+</sup> doped device is as high as 92%. Based on the SNN algorithm, the image recognition task was also successfully simulated and proved its advantage in energy consumption. Overall, the TFTs experimental results present a simple and low-cost method to enhance the synaptic characteristics of artificial synaptic TFT, which is expected to act as a basic computing unit in the next generation of the neuromorphic system and has the potential to give birth to better robots, self-driving cars, medical diagnosis, and other intelligent human-computer interaction systems.

### Conflicts of interest

There are no conflicts to declare.

#### Acknowledgements

This research was funded in part by the Natural Science Foundation of the Jiangsu Higher Education Institutions of China Program (19KJB510059), Natural Science Foundation of Jiangsu Province of China (BK20180242), the Suzhou Science and Technology Development Planning Project: Key Industrial Technology Innovation (SYG201924), University Research Development Fund (RDF-17-01-13), and the Key Program Special Fund in XJTLU (KSF-P-02, KSF-T-03, KSF-A-04, KSF-A-05, KSF-A-07, KSF-A-18).

#### References

- 1 J. Backus, Commun. ACM, 1978, 21, 613-641.

- 2 S. Z. Bisri, S. Shimizu, M. Nakano and Y. Iwasa, *Adv. Mater.*, 2017, **29**, 1607054.

- 3 R. Yu, E. Li, X. Wu, Y. Yan, W. He, L. He, J. Chen, H. Chen and T. Guo, ACS Appl. Mater. Interfaces, 2020, 12, 15446–15455.

- 4 D. Kuzum, S. Yu and H. S. Wong, *Nanotechnology*, 2013, 24, 382001.

- 5 L. Abbott and W. G. J. N. Regehr, Nature, 2004, 431, 796-803.

- 6 D. Seok Jeong, I. Kim, M. Ziegler and H. Kohlstedt, *RSC Adv.*, 2013, 3, 3169–3183.

- 7 K. C. Kwon, Y. Zhang, L. Wang, W. Yu, X. Wang, I.-H. Park,

H. S. Choi, T. Ma, Z. Zhu and B. Tian, *ACS Nano*, 2020, 7628–7638.

- 8 J. J. Harris, R. Jolivet and D. J. N. Attwell, *Neuron*, 2012, 75, 762–777.

- 9 B. Tang, S. Hussain, R. Xu, Z. Cheng, J. Liao and Q. Chen, ACS Appl. Mater. Interfaces, 2020, 12, 24920–24928.

- 10 Y. Liu, W. Yang, Y. Yan, X. Wu, X. Wang, Y. Zhou, Y. Hu, H. Chen and T. Guo, *Nano Energy*, 2020, 104930.

- 11 J. Park, M. Kwak, K. Moon, J. Woo, D. Lee and H. J. I. E. D. L. Hwang, *IEEE Electron Device Lett.*, 2016, **37**, 1559–1562.

- C. Y. Lin, J. Chen, P. H. Chen, T. C. Chang, Y. Wu,

J. K. Eshraghian, J. Moon, S. Yoo, Y. H. Wang,

W. C. Chen, Z. Y. Wang, H. C. Huang, Y. Li, X. Miao,

W. D. Lu and S. M. Sze, *Small*, 2020, 16, e2003964.

- 13 S. Boyn, J. Grollier, G. Lecerf, B. Xu, N. Locatelli, S. Fusil, S. Girod, C. Carrétéro, K. Garcia and S. J. N. C. Xavier, *Nat. Commun.*, 2017, 8, 1–7.

- 14 M.-K. Kim and J.-S. Lee, Nano Lett., 2019, 19, 2044-2050.

- 15 T. Tuma, A. Pantazi, M. Le Gallo, A. Sebastian and E. J. N. N. Eleftheriou, *Nat. Nanotechnol.*, 2016, **11**, 693.

- 16 Q. Wan, F. Zeng, J. Yin, Y. Sun, Y. Hu, J. Liu, Y. Wang, G. Li, D. Guo and F. J. N. Pan, *Nanoscale*, 2019, **11**, 5684–5692.

- 17 Y. Park, M.-K. Kim and J.-S. Lee, *J. Mater. Chem. C*, 2020, **8**, 9163–9183.

- 18 C. Li, D. Belkin, Y. Li, P. Yan, M. Hu, N. Ge, H. Jiang, E. Montgomery, P. Lin and Z. J. N. C. Wang, *Nat. Commun.*, 2018, 9, 1–8.

- 19 F. Alibart, L. Gao, B. D. Hoskins and D. B. J. N. Strukov, Nanotechnology, 2012, 23, 075201.

- 20 L. Gao, F. Alibart and D. B. Strukov, 2012 IEEE/IFIP 20th International Conference on VLSI and System-on-Chip (VLSI-SoC): IEEE, 2012, pp. 88–93.

- 21 L. Gao, P.-Y. Chen and S. J. I. E. D. L. Yu, *IEEE Electron Device Lett.*, 2015, **36**, 1157–1159.

- 22 L. Q. Guo, H. Han, L. Q. Zhu, Y. B. Guo, F. Yu, Z. Y. Ren, H. Xiao, Z. Y. Ge and J. N. Ding, *ACS Appl. Mater. Interfaces*, 2019, **11**, 28352–28358.

- 23 E.-K. Jang, Y. Park and J.-S. Lee, *Nanoscale*, 2019, **11**, 15382–15388.

- 24 S. Kim, Y. Lee, H.-D. Kim and S.-J. Choi, *Nanoscale*, 2020, **12**, 2040–2046.

- 25 Y. Liu, P. Guan, B. Zhang, M. L. Falk and H. E. Katz, *Chem. Mater.*, 2013, **25**, 3788–3796.

- 26 B. N. Pal, B. M. Dhar, K. C. See and H. E. Katz, *Nat. Mater.*, 2009, **8**, 898–903.

- 27 J. H. Lim, H.-J. Jeong, K.-T. Oh, D.-H. Kim, J. S. Park and J.-S. Park, *J. Alloys Compd.*, 2018, **762**, 881–886.

- 28 X. Xu, H. Wu, X. He, M. K. Hota, Z. Liu, S. Zhuo, H. Kim, X. Zhang and H. N. Alshareef, ACS Nano, 2020, 14, 9840–9847.

- 29 J. W. Park, B. H. Kang and H. J. Kim, *Adv. Funct. Mater.*, 2019, **30**, 1904632.

- 30 M. Demirci, 2015 IEEE 14th international conference on machine learning and applications (ICMLA): IEEE, 2015, pp. 1185–1190.

- 31 X. Zhang, J. Lu, Z. Wang, R. Wang, J. Wei, T. Shi, C. Dou, Z. Wu, J. Zhu, D. Shang, G. Xing, M. Chan, Q. Liu and M. Liu, *Sci. Bull.*, 2021, **66**, 1624–1633.

- 32 J. Hu, H. Tang, K. C. Tan and H. J. I. C. I. M. Li, *IEEE Comput. Intell. Mag.*, 2016, **11**, 56–68.

- 33 W. Wang, G. Pedretti, V. Milo, R. Carboni, A. Calderoni, N. Ramaswamy, A. S. Spinelli and D. J. S. A. Ielmini, *Sci. Adv.*, 2018, 4, eaat4752.

- 34 R. S. Zucker and W. G. Regehr, *Annu. Rev. Physiol.*, 2002, **64**, 355–405.

- 35 L. Zhang, J. Li, X. W. Zhang, X. Y. Jiang and Z. L. Zhang, *Appl. Phys. Lett.*, 2009, **95**, 072112.

- 36 S. Dai, Y. Wang, J. Zhang, Y. Zhao, F. Xiao, D. Liu, T. Wang and J. Huang, ACS Appl. Mater. Interfaces, 2018, 10, 39983–39991.

- 37 F. Yu, L. Q. Zhu, H. Xiao, W. T. Gao and Y. B. Guo, Adv. Funct. Mater., 2018, 28, 1804025.

- 38 X. Yang, J. Han, J. Yu, Y. Chen, H. Zhang, M. Ding, C. Jia, J. Sun, Q. Sun and Z. L. Wang, ACS Nano, 2020, 14, 8668–8677.

- 39 Y. He, Y. Yang, S. Nie, R. Liu and Q. Wan, J. Mater. Chem. C, 2018, 6, 5336–5352.

- 40 S. Dai, Y. Zhao, Y. Wang, J. Zhang, L. Fang, S. Jin, Y. Shao and J. Huang, *Adv. Funct. Mater.*, 2019, **29**, 1903700.

- 41 C. S. Yang, D. S. Shang, N. Liu, G. Shi, X. Shen, R. C. Yu, Y. Q. Li and Y. Sun, *Adv. Mater.*, 2017, **29**, 1700906.

- 42 J. Zhu, Y. Yang, R. Jia, Z. Liang, W. Zhu, Z. U. Rehman, L. Bao, X. Zhang, Y. Cai, L. Song and R. Huang, *Adv. Mater.*, 2018, **30**, e1800195.

- 43 C.-S. Yang, D.-S. Shang, N. Liu, E. J. Fuller, S. Agrawal, A. A. Talin, Y.-Q. Li, B.-G. Shen and Y. Sun, *Adv. Funct. Mater.*, 2018, 28, 1804170.

- 44 J. Zemek, P. Jiricek, O. Gedeon, B. Lesiak and A. Jozwik, *J. Non-Cryst. Solids*, 2005, 351, 1665–1674.

- 45 L. Zhou, S. Yang, G. Ding, J.-Q. Yang, Y. Ren, S.-R. Zhang, J.-Y. Mao, Y. Yang, Y. Zhou and S.-T. Han, *Nano Energy*, 2019, **58**, 293–303.

- 46 G. Ding, B. Yang, K. Zhou, C. Zhang, Y. Wang, J. Q. Yang, S. T. Han, Y. Zhai, V. A. L. Roy and Y. Zhou, *Adv. Electron. Mater.*, 2019, 6, 1900978.

- 47 J. Y. Du, C. Ge, H. Riahi, E. J. Guo, M. He, C. Wang, G. Z. Yang and K. J. Jin, *Adv. Electron. Mater.*, 2020, 6, 1901408.

- 48 J. Wang, Y. Li, Y. Yang and T.-L. Ren, *IEEE Electron Device Lett.*, 2017, 38, 588–591.

- 49 D. Choi, M.-K. Song, T. Sung, S. Jang and J.-Y. Kwon, *Nano Energy*, 2020, 74, 104912.

- 50 X. Liang, Z. Li, L. Liu, S. Chen, X. Wang and Y. Pei, *Appl. Phys. Lett.*, 2020, **116**, 012102.

- 51 Y. H. Liu, L. Q. Zhu, P. Feng, Y. Shi and Q. Wan, *Adv. Mater.*, 2015, 27, 5599–5604.

- 52 Y. Liu, J. Zhong, E. Li, H. Yang, X. Wang, D. Lai, H. Chen and T. Guo, *Nano Energy*, 2019, **60**, 377–384.

- 53 Y. Kim, A. Chortos, W. Xu, Y. Liu, J. Y. Oh, D. Son, J. Kang,

A. M. Foudeh, C. Zhu and Y. J. S. Lee, *Science*, 2018, 360, 998–1003.

- 54 Y. Li, Z. Xuan, J. Lu, Z. Wang, X. Zhang, Z. Wu, Y. Wang, H. Xu, C. Dou, Y. Kang, Q. Liu, H. Lv and D. Shang, *Adv. Funct. Mater.*, 2021, **31**, 2100042.

- 55 Y. Wang, Z. Lv, J. Chen, Z. Wang, Y. Zhou, L. Zhou, X. Chen and S. T. J. A. M. Han, *Adv. Mater.*, 2018, **30**, 1802883.

- 56 J. Yu, L. Liang, L. Hu, H. Duan, W. Wu, H. Zhang, J. Gao, F. Zhuge, T. Chang and H. J. N. E. Cao, *Nano Energy*, 2019, 62, 772–780.

- 57 S. Wang, C. Chen, Z. Yu, Y. He, X. Chen, Q. Wan, Y. Shi, D. W. Zhang, H. Zhou and X. J. A. M. Wang, *Adv. Mater.*, 2019, **31**, 1806227.

- 58 Z. Liu, S. Dai, Y. Wang, B. Yang, D. Hao, D. Liu, Y. Zhao, L. Fang, Q. Ou and S. J. A. F. M. Jin, *Adv. Funct. Mater.*, 2020, 30, 1906335.

- 59 K. Yang, S. Yuan, Y. Huan, J. Wang, L. Tu, J. Xu, Z. Zou, Y. Zhan, L. Zheng and F. J. N. F. E. Seoane, *npj Flexible Electron.*, 2018, 2, 1–9.

- 60 R. Xu, H. Jang, M.-H. Lee, D. Amanov, Y. Cho, H. Kim, S. Park, H.-J. Shin and D. J. N. L. Ham, *Nano Lett.*, 2019, **19**, 2411–2417.

- 61 L. Yin, C. Han, Q. Zhang, Z. Ni, S. Zhao, K. Wang, D. Li, M. Xu, H. Wu and X. J. N. E. Pi, *Nano Energy*, 2019, 63, 103859.

- 62 J. Zhu, Y. Yang, R. Jia, Z. Liang, W. Zhu, Z. U. Rehman,

L. Bao, X. Zhang, Y. Cai and L. J. A. M. Song, *Adv. Mater.*,

2018, 30, 1800195.

- 63 W. Xu, T. L. Nguyen, Y.-T. Kim, C. Wolf, R. Pfattner, J. Lopez, B.-G. Chae, S.-I. Kim, M. Y. Lee and E.-Y. Shin, *Nano Energy*, 2018, 48, 575–581.

- 64 W. Xu, S.-Y. Min, H. Hwang and T.-W. J. S. A. Lee, *Sci. Adv.*, 2016, **2**, e1501326.

- 65 T. Chen, X. Wang, D. Hao, S. Dai, Q. Ou, J. Zhang and J. Huang, *Adv. Opt. Mater.*, 2021, 9.

- 66 T. Ohno, T. Hasegawa, T. Tsuruoka, K. Terabe, J. K. Gimzewski and M. Aono, *Nat. Mater.*, 2011, 10, 591–595.

- 67 S. Wang, C. Chen, Z. Yu, Y. He, X. Chen, Q. Wan, Y. Shi, D. W. Zhang, H. Zhou, X. Wang and P. Zhou, *Adv. Mater.*, 2019, **31**, e1806227.

- 68 P.-Y. Chen, X. Peng and S. Yu, 2017 IEEE International Electron Devices Meeting (IEDM): IEEE, 2017, pp. 6.1.–6.1. 4.

- 69 H. Wang, Q. Zhao, Z. Ni, Q. Li, H. Liu, Y. Yang, L. Wang,

Y. Ran, Y. Guo, W. Hu and Y. Liu, *Adv. Mater.*, 2018,

30, e1803961.

- 70 J. Wall and C. Glackin, Front. Comput. Neurosci., 2013, 7, 182.

- 71 H. Hazan, D. J. Saunders, H. Khan, D. Patel, D. T. Sanghavi,

H. T. Siegelmann and R. Kozma, *Front. Neuroinf.*, 2018,

12, 89.

- 72 S. Song, K. D. Miller and L. F. Abbott, *Nat. Neurosci.*, 2000, 3, 919–926.

- 73 Z. Wang, S. Joshi, S. E. Savel'ev, H. Jiang, R. Midya, P. Lin, M. Hu, N. Ge, J. P. Strachan, Z. Li, Q. Wu, M. Barnell, G. L. Li, H. L. Xin, R. S. Williams, Q. Xia and J. J. Yang, *Nat. Mater.*, 2017, 16, 101–108.