# Nanoscale **Advances**

# PAPER

Check for updates

Cite this: Nanoscale Adv., 2023, 5, 4718

Received 5th June 2023 Accepted 13th July 2023 DOI: 10.1039/d3na00387f rsc.li/nanoscale-advances

### Introduction

Transition metal di-chalcogenides (TMDCs) are a family of twodimensional (2D)-layered materials with a chemical formula of  $MX_2$  (M = Mo, W, Ti, Nb, V, etc. and X = S, Se, Te).<sup>1,2</sup> 2D TMDCs constitute a wide library of compounds ranging from semiconductors and (semi)metals to superconductors.<sup>3</sup> Among semiconducting 2D TMDCs, MoS<sub>2</sub> is the most widely explored material because of its abundance in nature and its outstanding electronic properties.<sup>4,5</sup> Field-effect transistors (FETs) based on  $MoS_2$  demonstrate high current densities of 700–1135  $\mu A$  $\mu$ m<sup>-1</sup>,<sup>6-8</sup> high ON/OFF current ratios in the range of 10<sup>7</sup>–10<sup>9</sup>,<sup>5,9,10</sup> low subthreshold swing (SS) values close to the thermionic limit  $(\sim 60 \text{ mV dec}^{-1})$ ,<sup>11,12</sup> reasonably good mobility,<sup>5,13,14</sup> decent reliability,9 relatively low variability15 and compatibility with conventional Si processing technologies.16-18 These fascinating features of MoS<sub>2</sub> FETs may open new horizons for ultra-scaled nanoelectronic devices and circuits.19,20

<sup>b</sup>Department of Physics and Nanotechnology, Laboratory for Advanced Nanoelectronic Devices, SRM Institute of Science and Technology, SRM Nagar, Kattankulathur, 603 203, Tamil Nadu, India. E-mail: abhaya@srmist.edu.in

# ALD-grown two-dimensional TiS<sub>x</sub> metal contacts for MoS<sub>2</sub> field-effect transistors<sup>†</sup>

Reyhaneh Mahlouji, 🕩 \*\* Wilhelmus M. M. (Erwin) Kessels, 🕩 \* Abhay A. Sagade 🕩 \*\* and Ageeth A. Bol (1)\*\*

Metal contacts to MoS<sub>2</sub> field-effect transistors (FETs) play a determinant role in the device electrical characteristics and need to be chosen carefully. Because of the Schottky barrier (SB) and the Fermi level pinning (FLP) effects that occur at the contact/MoS<sub>2</sub> interface, MoS<sub>2</sub> FETs often suffer from high contact resistance  $(R_c)$ . One way to overcome this issue is to replace the conventional 3D bulk metal contacts with 2D counterparts. Herein, we investigate 2D metallic TiS<sub>x</sub> ( $x \sim 1.8$ ) as top contacts for MoS<sub>2</sub> FETs. We employ atomic layer deposition (ALD) for the synthesis of both the  $MoS_2$  channels as well as the  $TiS_x$ contacts and assess the electrical performance of the fabricated devices. Various thicknesses of TiS<sub>x</sub> are grown on MoS<sub>2</sub>, and the resultant devices are electrically compared to the ones with the conventional Ti metal contacts. Our findings show that the replacement of 5 nm Ti bulk contacts with only ~1.2 nm of 2D TiS<sub>x</sub> is beneficial in improving the overall device metrics. With such ultrathin TiS<sub>x</sub> contacts, the ONstate current ( $I_{ON}$ ) triples and increases to ~35  $\mu$ A  $\mu$ m<sup>-1</sup>.  $R_c$  also reduces by a factor of four and reaches  $\sim$ 5 M $\Omega$  µm. Such performance enhancements were observed despite the SB formed at the TiS<sub>x</sub>/MoS<sub>2</sub> interface is believed to be higher than the SB formed at the Ti/MoS<sub>2</sub> interface. These device metric improvements could therefore be mainly associated with an increased level of electrostatic doping in MoS<sub>2</sub>, as a result of using 2D TiS<sub>x</sub> for contacting the 2D MoS<sub>2</sub>. Our findings are also well supported by TCAD device simulations.

> Implementation of MoS<sub>2</sub> or any other 2D TMDC into mainstream technology platforms is not without hurdles. 2D FETs generally suffer from high contact resistance  $(R_c)$ <sup>21</sup> which is still above the requirements specified by the International Roadmap for Devices and Systems (IRDS).<sup>22</sup> High R<sub>c</sub> originates from the unavoidable Schottky barrier (SB) formation and Fermi level pinning (FLP) effect at the metal-semiconductor (M-S) junctions.<sup>23,24</sup> In recent years, several attempts have been made to tackle high R<sub>c</sub> in 2D FETs, namely substitutional/chemical doping of the 2D layer,25,26 2D phase engineering at the contact regions,<sup>27</sup> the insertion of oxide buffer layers (Ta<sub>2</sub>O<sub>3</sub>, Al<sub>2</sub>O<sub>3</sub>) below the contacts,<sup>28,29</sup> electrostatically doping the 2D channel by high-k dielectrics,6,10,30 switching to edge contact device geometry (rather than using the conventional top contact device geometry)<sup>31-34</sup> and utilization of semi-metal,8 graphene32,35-38 or metallic 2D TDMC contacts.<sup>34,39,40</sup> To date, the lowest  $R_c$  records are in the range of 123–520  $\Omega$  µm, being held for semi-metal<sup>8</sup> or graphene contacts,37 phase engineering the 2D layer at the contact areas,27 dielectric mediated charge transfer doping of the 2D channel<sup>6</sup> and metallic 2D TMDC employment in edge contact device geometry.34

> Among the above-mentioned methods for reducing  $R_{c}$ , the usage of 2D metallic contacts, such as VS2,<sup>34</sup> VSe2<sup>39</sup> or NbS<sub>2</sub><sup>40</sup> in 2D FETs has lately gained a surging interest.

View Article Online

View Journal | View Issue

<sup>&</sup>lt;sup>a</sup>Department of Applied Physics, Eindhoven University of Technology, P. O. Box 513, 5600 MB, Eindhoven, The Netherlands. E-mail: r.mahlouji@tue.nl; a.a.bol@tue.nl

<sup>†</sup> Electronic supplementary information (ESI) available. See DOI: https://doi.org/10.1039/d3na00387f

#### Paper

Conventional bulk metallic contacts are known to form covalent bonds with the 2D semiconducting layer,<sup>41</sup> leading to charge redistribution at the M-S junction, work function (WF) modulations and metal-induced gap state (MIGS)<sup>42</sup> formation as well as 2D electronic band-structure perturbation that altogether result in high SB/strong FLP<sup>14,41-43</sup> and therefore an overall high  $R_{\rm c}$ . 2D metallic contacts, on the other hand, offer several advantages over the 3D bulk counterparts. First and foremost, they only weakly bind/react with 2D semiconductors. This is mainly because of the overall weak van der Waals (vdW) interactions that leads to an almost clean and flat vdW interface at the 2D-2D M-S junctions, wherein lattice matching becomes less important.44 Such vdW interactions are also shown to suppress MIGS and allow for an almost unperturbed 2D semiconductor electronic band-structure, weaker FLP and lower Rc.45 Second, the WF in 2D metals can be modulated by the application of an external electric field, enabling the control of Schottky barrier height (SBH) formed at the 2D M-S junctions.45,46

The other challenge ahead of integrating metallic and/or semiconducting 2D TMDCs into nanoelectronic devices and circuits is their high quality and large-scale synthesis. Among the different synthesis methods, chemical vapor deposition (CVD) is shown to be one of the most promising techniques for the growth of 2D TMDCs, as it ensures the delivery of premium quality films over large areas.<sup>13,47-51</sup> However, the high thermal budget that is often used in CVD may be a concern for the semiconductor industry. In addition, realization of vdW heterostructures made from 2D metals and semiconductors by using CVD, in both edge and top contact device geometries, typically involves complex procedures.<sup>34,39,40</sup>

In recent years, atomic layer deposition (ALD) has drawn attention for the growth of not only single layer 2D TMDCs<sup>52-55</sup> but also their heterostructures (both in lateral<sup>56</sup> and horizontal directions<sup>57</sup>). ALD is a low-temperature thin-film cyclic synthesis technique which is highly compatible with conventional Si technologies and excels in large area uniformity, thickness control down to sub-monolayer regime as well as conformality for high aspect ratio features.<sup>58,59</sup>

In this work, we employ ALD for the growth of both 2D metallic and 2D semiconducting layers and introduce a straightforward approach for the fabrication of 2D-based FETs. We chose  $TiS_x$  ( $x \sim 1.8$ ) as the contacts and  $MoS_2$  as the semiconducting channel material. TiS<sub>2</sub> is one member of the 2D TMDC family with (semi)metallic60 properties. Theoretically, it has been shown that if employed as the contact electrodes, TiS<sub>2</sub> forms Schottky (Ohmic) contacts with n-type (p-type) MoS<sub>2</sub>,<sup>61</sup> due to its high WF ( $\sim$ 5.7 eV).<sup>45,62,63</sup> In addition, it preserves the MoS<sub>2</sub> intrinsic properties, meanwhile delivering high electrical conductivities.<sup>61</sup> During our study, we compare ALD grown TiS<sub>x</sub> contacts of various thicknesses with evaporated conventional Ti counterparts. We demonstrate that the fabricated MoS<sub>2</sub> FETs with  $\sim 1.2$  nm thick TiS<sub>x</sub> contacts outperform the ones with Ti contacts, as the overall MoS<sub>2</sub> FET device figures of merit (e.g. the maximum current density ( $I_{ON}$ ), field-effect mobility ( $\mu_{FE}$ ) and  $R_{\rm c}$ ) improve when such ultrathin layers of TiS<sub>x</sub> contacts are utilized.

## Experimental

#### MoS<sub>2</sub> film synthesis

A two-step approach was followed for the synthesis of  $MoS_2$ , whereby ~1.5 nm  $MoO_x$  was initially grown using plasmaenhanced (PE-)ALD at 50 °C,<sup>64</sup> in an Oxford Instruments Plasma Technology (FlexAL) ALD reactor, on degenerately doped ( $p^{++}$ ) Si substrates that were covered with ~87 nm SiO<sub>2</sub>. The as-deposited  $MoO_x$  films were then sulfurized in a homebuilt tube furnace, where a gas mixture of H<sub>2</sub>S/Ar (10%/90%) was introduced at 900 °C for 45 min, resulting in ~1.2 nm thick  $MoS_2$  films. Further details of the synthesis conditions and the  $MoS_2$  film specifications are reported in ref. 57 and 65.

#### TiS<sub>x</sub> contact synthesis

Direct thermal ALD was employed for the growth of  $TiS_x$ contacts with various thicknesses at 100 °C. The deposition took place in the FlexAL reactor. Tetrakis (dimethyl amido) titanium (TDMAT) (Sigma-Aldrich Chemie BV, 99.999% pure) was chosen as the precursor. During the first half cycle of ALD, TDMAT was dosed into the reaction chamber for 4.2 s with Ar carrier gas, at a pressure of 80 mTorr, followed by a 20 s Ar purge step with a flow rate of 300 sccm, at the lowest achievable reaction chamber pressure (~7 mTorr). In the second ALD half cycle, H<sub>2</sub>S/Ar gas mixture was introduced as the co-reactant for 30 s, with a flow rate of 10/40 sccm and at 80 mTorr, followed by another Ar purge step (with similar conditions mentioned above). More information regarding the  $TiS_x$  synthesis on  $SiO_2$ or on 2D TMDC substrates as well as TiS<sub>r</sub> film specifications (e.g. TiS<sub>x</sub> chemical composition, plane orientation, morphology, electrical resistivity and etc.) can be found in previous studies.56,66

#### Film thickness measurements

During the PE-ALD of  $MoO_x$  and thermal ALD of  $TiS_x$ , the film thicknesses were measured by *in situ* spectroscopic ellipsometry (SE) (J. A. Woollam Co., Inc. M-2000FI, 0.75–5 eV). From the obtained data, the growth per cycle (GPC) was determined. The final  $MoS_2$  film thickness was also verified using *ex situ* SE (J. A. Woollam Co., Inc. M-2000D, 1.25–6.5 eV). All the collected data were analyzed using complete EASE software and its embedded B-spline oscillator model.

#### **Device fabrication**

Standard electron beam lithography (EBL) was carried out for the fabrication of back-gate  $MoS_2$  FETs, and PMMA was used as the electron sensitive resist. Details of the device fabrication are described in ref. 67. During the first EBL step, contact regions were defined on the PMMA coated  $MoS_2$ . Various thicknesses of  $TiS_x$  were then grown by thermal ALD on the PMMA opening areas, in the FlexAL reactor and at 100 °C. Choosing such a low deposition temperature ensures that PMMA does not evaporate during the growth of  $TiS_x$ . Immediately after the  $TiS_x$  growth, the samples were transferred into an electron beam (e-beam) evaporation chamber, where an Au layer of maximum 95 nm was deposited. The Au deposition is to facilitate probing the contacts during the electrical measurements. For the reference case, 5/95 nm of Ti/Au<sup>67</sup> was e-beam evaporated in the contact openings (with similar conditions as of the Au layer on the ALD grown TiS<sub>x</sub>). Next, the lift-off process was carried out by submerging the samples in acetone overnight. For defining the channel regions and isolating the individual blocks, a second EBL step was required, followed by MoS<sub>2</sub> dry etching from the opened areas using SF<sub>6</sub>/O<sub>2</sub> plasma gas mixture in an Oxford Instruments Reactive Ion Etching (RIE) reactor. Finally, PMMA was removed in acetone, and the fabricated devices were immediately capped with 5/25 nm of thermal ALD AlO<sub>x</sub><sup>68</sup>/PE-ALD HfO<sub>x</sub>,<sup>69</sup> both processed at 100 °C.

#### **Electrical characterization**

Current–voltage (*I–V*) measurements were performed in a cryogenic probe station (Janis ST-500) at a base pressure of  $\sim$ 1.9 × 10<sup>-4</sup> mbar and with a Keithley 4200-SCS parameter analyzer.

#### **Device simulations**

Technology computer-aided design (TCAD) simulations were carried out using SILVACO, and standard semiconductor physics transport equation solutions were obtained by the Newton method. The simulation parameters were selected in accordance with the experimental data.

### Results and discussion

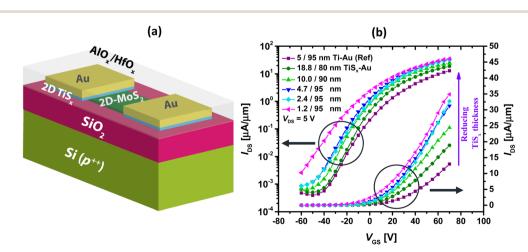

Series of  $\text{TiS}_x$  thicknesses ranging from ~20 nm down to ~1.2 nm were grown as the contacts to  $\text{MoS}_2$  using thermal ALD at 100 °C. For the ease of probing the contacts during the *I–V* measurements, an Au layer of maximum 95 nm was evaporated on top of  $\text{TiS}_x$ . The electrical performance of the fabricated devices were assessed and compared to a reference device, for which 5/95 nm of Ti/Au was employed as the contacts. As per a previous report,<sup>67</sup> this thickness combination is found to be the most optimal for the Ti/Au stacks contacted to the ALD-

based  $MoS_2$  films. Fig. 1(a) shows the schematics of the fabricated devices.

The transfer curves  $(I_{DS}-V_{GS})$  of the MoS<sub>2</sub> FETs with different  $TiS_x$  contact thicknesses are also provided in Fig. 1(b) and compared to the reference device. In all the cases, the current is measured on 500 nm long MoS<sub>2</sub> channels and normalized to the device width  $(1 \mu m)$ . At first sight, it is explicit that the entire series of TiS<sub>x</sub>-contacted devices outperform the reference case. In addition, reducing the  $TiS_x$  thickness from 20 nm down to 1.2 nm improves the overall electrical performance. The maximum ON-state current ( $I_{ON}$ ) increases to ~35 µA µm<sup>-1</sup> for the  $MoS_2$  FETs with the thinnest  $TiS_x$  contacts, which is nearly three times higher than that of the reference. Furthermore, the threshold voltage  $(V_{\rm T})$  shifts negatively with reducing the TiS<sub>x</sub> thickness, and the OFF-state current  $(I_{OFF})$  increases for the thinnest  $TiS_x$  contacts of ~1.2 nm, both implying an increase in the MoS<sub>2</sub> doping level.<sup>12,70</sup> Such doping effects have also been observed in previous studies where other 2D metallic contacts (e.g. graphene,<sup>36,38</sup> NbS<sub>2</sub><sup>40</sup> or VSe<sub>2</sub><sup>39</sup> have been utilized. We note that in general, any kind of metal (2D or 3D bulk) dopes MoS<sub>2</sub> or other 2D semiconductors up to a certain extent.41,61,70,71

For verifying the repeatability of the observations shown in Fig. 1(b), another set of  $MoS_2$  FETs with series of  $TiS_x$  contact thicknesses were fabricated and characterized. Similar trends were observed for the second set upon reducing the  $TiS_x$  contact thickness. See Fig. S1(a) and (b) in the ESI<sup>†</sup> and the associated discussion.

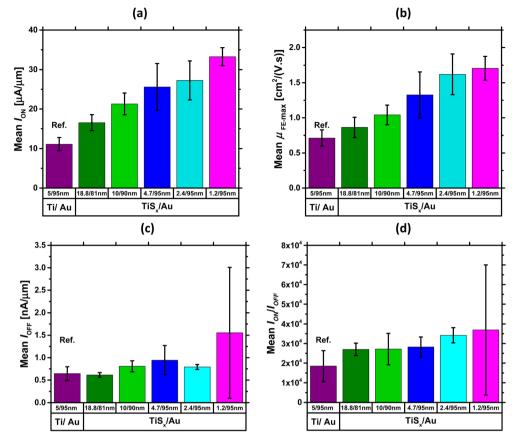

To further gain insight into the overall electrical performance of the MoS<sub>2</sub> FETs with TiS<sub>x</sub> contacts, the average statistical data of  $I_{ON}$ , maximum  $\mu_{FE}$ ,  $I_{OFF}$  and ON/OFF current ratio are provided in Fig. 2(a)–(d), respectively. The presented data were obtained by measuring three-four devices on each studied sample.

In Fig. 2(a) and (b),  $I_{ON}$  and the maximum  $\mu_{FE}$  show a monotonically increasing trend with reducing the TiS<sub>x</sub> thickness. In addition, the devices with the thickest TiS<sub>x</sub> contacts (~20 nm) still outperform the reference devices of ~5 nm Ti. Both values ( $I_{ON}$  and maximum  $\mu_{FE}$ ) also increase nearly twice

Fig. 1 (a) Schematics of the fabricated  $MoS_2$  FETs, (b) measured transfer curves of the devices with series of  $TiS_x$  contact thicknesses, in both semilog and linear scales. Data for the reference sample is also provided.

Fig. 2 Average statistical data of (a)  $I_{ON}$ , (b) maximum  $\mu_{FE}$ , (c)  $I_{OFF}$  and (d) ON/OFF current ratio for the MoS<sub>2</sub> FETs with various TiS<sub>x</sub> thicknesses, all obtained at  $V_{DS} = 5$  V. Data for the reference case with Ti/Au contacts is also included.

on average when the  $TiS_x$  thickness reduces to ~1.2 nm. These observed device performance improvements by reducing the TiS<sub>x</sub> contact thickness can be mainly attributed to the reduction of the interfacial tunneling barrier within  $TiS_x$ , which leads to a reduction in the TiS<sub>r</sub> overall interlayer resistance.<sup>61</sup> In fact, because layers in 2D TMDCs are generally held by weak vdW forces, a gap is always present in between the individual layers. This gap acts as an interfacial tunneling barrier that scatters carriers, degrades the current and contributes to  $R_{\rm c}$ .<sup>41,61,72,73</sup> Therefore, when the number of layers in a 2D metallic  $TiS_x$ reduces, the interfacial tunneling barrier and the resulting interlayer resistance are expected to reduce. In addition to that, the Au electrodes get closer to the MoS<sub>2</sub> active layers, altogether leading to a more efficient carrier injection/collection and hence improvements in the ON-state device characteristics. The overall superior performance of the TiS<sub>x</sub>-contacted MoS<sub>2</sub> FETs to the reference devices can also be associated with the reduced perturbance of the MoS<sub>2</sub> electronic band-structure,<sup>45</sup> when the 3D bulk metallic contacts (Ti) are replaced with the 2D  $TiS_x$ counterparts.

Fig. 2(c) shows the average trend for  $I_{OFF}$ . As can be seen, there is no significant change in this metric with reducing the TiS<sub>x</sub> thickness, except for when ~1.2 nm TiS<sub>x</sub> contacts are employed. The rise of  $I_{OFF}$  in this case can be associated with the increased electrostatic doping in MoS<sub>2</sub>, such that higher back-

gate voltages are required to fully deplete the channel in the OFF-state regime. However, because  $I_{\rm OFF}$  is maintained well below 2  $\mu$ A  $\mu$ m<sup>-1</sup>, a similar ON/OFF current ratio in the range of 10<sup>4</sup> (Fig. 2(d)) is achieved for all the studied cases. It is worth-while mentioning that  $I_{\rm OFF}$  can be further controlled if a thinner back-gate oxide (*e.g.* 30 nm SiO<sub>2</sub>) is employed, as thinner SiO<sub>2</sub> typically leads to improved electrostatic control over the MoS<sub>2</sub> channel.

Based on the analyses provided so far, the  $MoS_2$  FETs with ~1.2 nm thick  $TiS_x$  contacts were found to be the most optimally operating devices. To confirm this further, the electrical performance of the second set of  $MoS_2$  devices with various  $TiS_x$  contact thicknesses were also statistically evaluated. See Fig. S1(a)–(d) in the ESI.† Our analyses verify that the  $MoS_2$  devices with ~1.2 nm thick  $TiS_x$  contacts still lead to the most optimal performance. Therefore, they were selected for further electrical characterization.

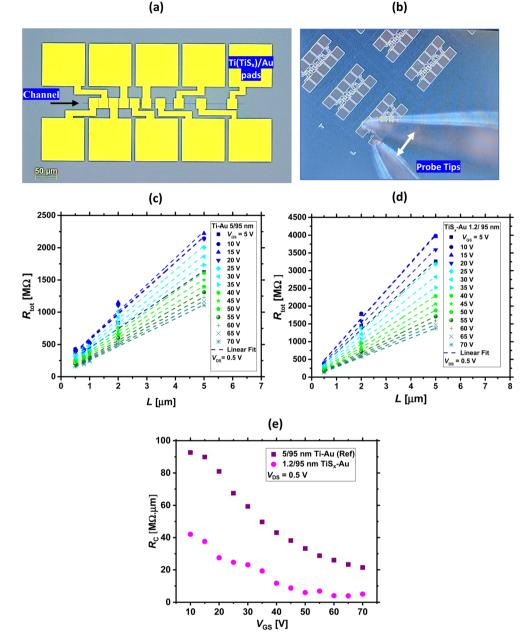

The  $R_c$  of such devices were evaluated in the next step and compared to that of the reference case. To extract  $R_c$ , transfer length method (TLM) structures<sup>74</sup> of various MoS<sub>2</sub> channel lengths (ranging from 0.5–5 µm) were electrically measured, and the total resistance ( $R_{tot}$ ) of both TiS<sub>x</sub> and Ti contacts were extracted from the transfer curves. Fig. 3(a) and (b) show the layout TLM design and the optical image of the probed TLM structures used for the *I–V* measurements, respectively.

Fig. 3 (a) Top-view TLM layout design used for  $R_c$  extractions, with a channel width of 1  $\mu$ m and various channel lengths ranging from 0.5–50  $\mu$ m. As indicated, yellow squares are the Ti(TiS<sub>x</sub>)/Au contact pads. (b) Optical image of the probed TLM structures used for the *I*–*V* measurements. The white arrow indicates the probe tips. (c) and (d)  $R_{tot}$  versus *L* for the MoS<sub>2</sub> FETs with TiS<sub>x</sub>/Au and Ti/Au contacts, respectively (at  $V_{DS} = 0.5$  V and for different  $V_{GS}$ ). (e) Extracted  $R_c$  as a function of  $V_{GS}$  for the TiS<sub>x</sub>/Au and Ti/Au cases.

A low  $V_{\rm DS}$  voltage ( $V_{\rm DS} = 0.5$  V) was applied for the  $R_{\rm c}$  evaluations. This was to minimize the errors occurring during the  $R_{\rm c}$  extraction, as the application of high  $V_{\rm DS}$  ( $V_{\rm DS} > 1$  V) resulted in negative  $R_{\rm c}$  and its underestimation. The  $R_{\rm c}$  values were obtained using the following formula, where the dependence of the individual parameters on the applied  $V_{\rm GS}$  is also included:<sup>74,75</sup>

$$R_{\rm tot}(V_{\rm GS}) = 2 \times R_{\rm c}(V_{\rm GS}) + R_{\rm sh}(V_{\rm GS}) \times (L/W) \tag{1}$$

Here,  $R_{\rm sh}$  is the channel sheet resistance, and *L* and *W* are channel length and width, respectively.

Fig. 3(c) and (d) display  $R_{tot}$  as a function of L for the TiS<sub>x</sub> contacts and the reference case, respectively, at  $V_{DS} = 0.5$  V and for different  $V_{GS}$  values. Using these plots,  $R_c$  can be extracted.<sup>74</sup> This is provided in Fig. 3(e). As can be seen, at  $V_{GS} = 70$  V, the  $R_c$  for the TiS<sub>x</sub>-contacted MOS<sub>2</sub> FETs is ~5.0 M $\Omega$  µm and nearly four times smaller than that of the reference (which is 21.4 M $\Omega$  µm). These values of  $R_c$  are still higher than what is obtained for FETs fabricated from exfoliated/CVD grown highly crystalline MoS<sub>2</sub>, which may be due to the nanocrystalline nature of our films and

their average grain size of 70 nm.<sup>57</sup> However, the replacement of 3D bulk Ti contacts with the 2D  $\text{TiS}_x$  counterparts is overall beneficial in reducing  $R_c$  of the ALD-based MoS<sub>2</sub> FETs.

One might also wonder about the  $R_{\rm sh}$  of the ALD-based MoS<sub>2</sub>. It is worthwhile mentioning that for having an accurate estimation of  $R_{\rm sh}$ , 4-wire measurements<sup>76</sup> as well as models specifically tailored for 2D polycrystalline materials<sup>77,78</sup> need to be employed.

The SBH is another important factor for evaluating the contact quality in 2D-based FETs. The carrier transport across a Schottky junction can be described by thermionic emission equation modified for 2D materials:<sup>21,79</sup>

$$I_{\rm DS} = AA_{\rm 2D}^* T^{3/2} \exp((-q\varphi_{\rm Bn})/(k_{\rm B}T))[1 - \exp((-qV_{\rm DS})/(\eta K_{\rm B}T))]$$

(2)

in this equation, *A* is the contact area,  $A_{2D}^*$  is the 2D equivalent Richardson constant, *T* is temperature, *q* is the elementary charge magnitude,  $k_{\rm B}$  is the Boltzmann constant,  $\varphi_{\rm Bn}$  is the effective barrier height for electrons and  $\eta$  is the ideality factor. To determine  $\varphi_{\rm Bn}$  of both TiS<sub>x</sub> and Ti contacts to MoS<sub>2</sub>, lowtemperature *I*-*V* measurements were carried out. The output data  $(I_{\rm DS}-V_{\rm DS})$  were obtained for various  $V_{\rm GS}$  (ranging from -10 V to +60 V), at seven different temperatures (180–290 K). A first order approximation of eqn (2) was used,<sup>81</sup> which is expressed as the following:

$$I_{\rm DS} \approx AA_{\rm 2D}^* T^{3/2} \exp[(-q/(k_{\rm B}T))(\varphi_{\rm Bn} - V_{\rm DS}/\eta)]$$

(3)

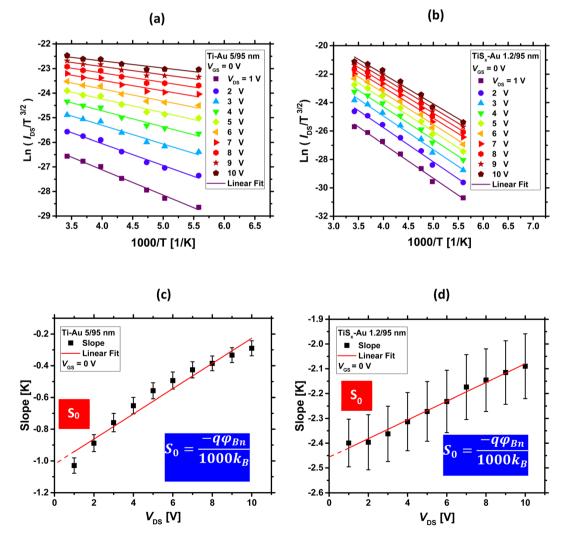

For a fixed  $V_{\rm GS}$ ,  $\ln(I_{\rm DS}/T^{3/2})$  versus 1000/*T* is first plotted at each measured  $V_{\rm DS}$ , and a series of Arrhenius plots are obtained. This is shown in Fig. 4(a) and (b) for both Ti/Au and TiS<sub>x</sub>/ Au cases, respectively. As can be seen, the acquired data are linear in each  $V_{\rm DS}$ . If the slope of the individual fitted lines are plotted as a function of  $V_{\rm DS}$ , as illustrated in Fig. 4(c) and (d) for both the TiS<sub>x</sub> and Ti cases, the interception point with the vertical axis (S<sub>0</sub>) yields  $\varphi_{\rm Bn}$  for a fixed  $V_{\rm GS}$ .<sup>80,81</sup> S<sub>0</sub> is related to  $\varphi_{\rm Bn}$ through the following equation:<sup>81</sup>

$$S_0 = (-q\varphi_{\rm Bn})/(1000k_{\rm B}) \tag{4}$$

Fig. 4 Arrhenius plots for (a) Ti/Au and (b) TiS<sub>x</sub>/Au contacts to MoS<sub>2</sub> at  $V_{GS} = 0$  V, (c) and (d) extracted slopes from (a) and (b) as a function of  $V_{DS}$ , at  $V_{GS} = 0$  V. The vertical axis-intercept (S<sub>0</sub>) yields  $\varphi_{Bn}$  at  $V_{GS} = 0$  V.

#### Nanoscale Advances

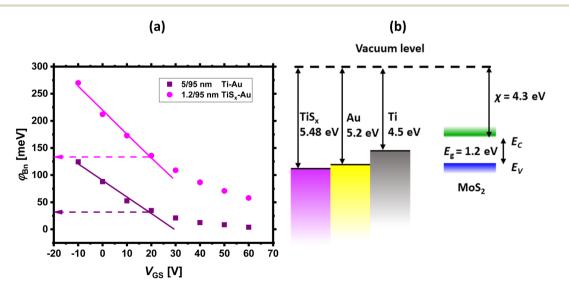

If the above-mentioned extractions are repeated for each measured  $V_{\rm GS}$ ,  $\varphi_{\rm Bn}$  as a function of  $V_{\rm GS}$  can be obtained. The final results are shown in Fig. 5(a). As evidenced from this figure,  $\varphi_{\rm Bn}$  varies linearly at low  $V_{\rm GS}$  ranges (the fitted straight line). Then, it starts to deviate from the linearity at a certain  $V_{\rm GS}$ . In fact, the thermionic emission equation is valid only for  $V_{\rm GS}$  below the flat-band potential ( $V_{\rm FB}$ ).<sup>23</sup> Above  $V_{\rm FB}$ , in addition to the thermionic emission, the tunneling emission contributes to the total current, leading to the observed deviation from the linear trend.<sup>14</sup>

Fig. 5(a) also compares the contact metal types. For all the measured  $V_{\text{GS}}$ ,  $\varphi_{\text{Bn}}$  is higher for the TiS<sub>x</sub> contacts (270–132 meV) than for the Ti counterparts (123–35 meV). This is expected, as TiS<sub>x</sub> is theoretically predicted to have higher WF than Ti. To illustrate this concept, the energy band diagrams of Ti, TiS<sub>x</sub> and Au are schematically depicted in Fig. 5(b).

Despite a higher  $\varphi_{Bn}$ , the TiS<sub>x</sub> contacts to MoS<sub>2</sub> exhibit lower  $R_{\rm c}$  than the Ti counterparts (Fig. 3(e)). Therefore, the observed  $R_{\rm c}$  reduction in the TiS<sub>x</sub>-contacted devices is mostly associated with an increase in the MoS<sub>2</sub> electrostatic doping level, which could be due to the achievement of a flat/clean interface at the junction upon replacing the 3D Ti contacts with the 2D  $TiS_r$ counterparts, such that the carriers are injected more efficiently into the MoS<sub>2</sub> channel. The increase in the MoS<sub>2</sub> n-type doping level is evidenced from the negative shift of  $V_{\rm T}$ (Fig. 1(b)) and the slight increase of  $I_{OFF}$  (Fig. 1(b) and 2(c)), once the Ti contacts are replaced with  $\sim 1.2$  nm of TiS<sub>x</sub>. For high doping levels, the width of the SB reduces,<sup>23</sup> and the carrier tunneling towards MoS<sub>2</sub> further facilitates, leading to an overall increase in the current. In such a situation, the height of the SB ( $\varphi_{Bn}$ ) will have a smaller effect on the overall device performance.

Considering  $TiS_x$  contacted  $MoS_2$  FETs, one might find the observations contradictory to the energy band diagram analysis, as high WF metals (such as  $TiS_x$ ) are expected to dope  $MoS_2$  to p-

type. Recent density functional theory (DFT) calculations by Gao et al.<sup>61</sup> have addressed this controversy and have shown that TiS<sub>2</sub> can act as both p- or n-type contact to MoS<sub>2</sub>, depending on the TiS<sub>2</sub> number of layers and the doping concentration of both materials. TiS<sub>2</sub> can also tune the barrier height at the junction, and it is predicted that for n-type 2L-TiS<sub>2</sub> (~1.2 nm) contacts to MoS<sub>2</sub>, the barrier height for electrons is two-times smaller than for holes. Hence, in contrast to the current band theory, it is possible to ignore p-type doping of MoS<sub>2</sub> by TiS<sub>x</sub> contacts. Similar experimental observations were also reported by Bark et al.<sup>40</sup> when replacing 3D Mo contacts (WF ~ 4.5 eV) with high WF 2D NbS<sub>2</sub> contacts (WF ~ 6.1 eV)<sup>45</sup> in MoS<sub>2</sub> FETs. These studies indicate that there is a clear distinction between 3D and 2D metals contacting 2D semiconductors.

It is also worthwhile mentioning that for ultrathin layers of 2D  $\text{TiS}_x$ , quantum confinement effects start to play a role, which can affect the  $\text{TiS}_x$  electronic band structure and its alignment to that of  $\text{MoS}_2$  at the interface. Hence, providing a more realistic picture of the  $\text{TiS}_x/\text{MoS}_2$  energy band diagrams may require additional DFT simulations.

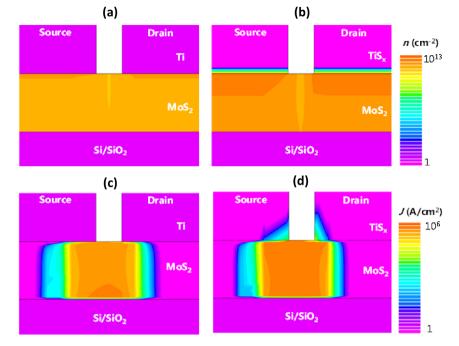

To further understand the discrepancies between the 2D and 3D metals contacting a 2D TMDC semiconductor and to verify our experimental results, TCAD simulations were also performed for the 2D TiS<sub>2</sub> and 3D Ti contacts to MoS<sub>2</sub>. The simulated device had a channel length of 500 nm and consisted of 1.2 nm of MoS<sub>2</sub>, 5 nm of Ti and 1.2 nm of TiS<sub>2</sub>. Selection of 1.2 nm TiS<sub>2</sub> was because this thickness led to the most optimally performing MoS<sub>2</sub> FETs in our experiments. The biasing conditions were  $V_{DS} = 1$  V and  $V_{GS} = 30$  V, to ensure that both device types are fully in their ON-state regime. Further details regarding the simulation parameters are provided in the ESI, Section S.3.† The resultant 2D contour plots of the gate-field-induced charge carrier density and the current density are displayed in Fig. 6(a)–(d), respectively. We note that Au contact pads are not shown in these figures.

Fig. 5 (a) Effective Schottky barrier height ( $\varphi_{Bn}$ ) as a function of  $V_{GS}$  for both Ti/Au and TiS<sub>x</sub>/Au contacts to MoS<sub>2</sub> FETs. Below the flat band condition,  $\varphi_{Bn}$  reduces linearly with increasing  $V_{GS}$ , which is marked by the fitted straight lines in both contact cases, (b) energy band diagrams of Ti, sulfur-deficient TiS<sub>x</sub><sup>62</sup> and Au with respect to MoS<sub>2</sub>.

Fig. 6 (a and b) 2D contour plots of the induced charge carrier density and (c and d) current density for Ti and TiS<sub>2</sub> contacts to MoS<sub>2</sub>, respectively. Simulations were performed for 1.2 nm of MoS<sub>2</sub>, 5 nm of Ti and 1.2 nm of TiS<sub>2</sub> at  $V_{DS} = 1$  V and  $V_{GS} = 30$  V.

As can be seen from Fig. 6(a) and (b), when  $TiS_2$  is in contact with  $MoS_2$ , more charges are induced into the channel and  $MoS_2$  is doped to a higher extent, compared to the Ti case. The increase in the induced charge carrier density close to the contact regions can be distinguished by the dark orange color. As anticipated, the transverse field-induced carrier formation can be observed at the  $TiS_2$ - $MoS_2$  interface as well. Comparing Fig. 6(c) and (d), an increase in the  $MoS_2$  current density can be noted for the case of  $TiS_2$ . In fact, only a small portion of  $TiS_2$  is actively in contact with  $MoS_2$ , which facilitates the charge transport and subsequently leads to improved current density as well as the overall reduction of  $R_c$ . The provided simulation results well confirm the experimental observations and highlight the importance of integrating 2D metallic contacts with 2D semiconductors in 2D-based FETs.

## Conclusions

To conclude, in this study, we have investigated the integration of 2D metallic TiS<sub>x</sub> with semiconducting 2D MoS<sub>2</sub> by using atomic layer deposition (ALD). We have shown that ALD grown TiS<sub>x</sub> ( $x \sim 1.8$ ) contacts can improve the overall electrical performance of ALD-based MoS<sub>2</sub> FETs, when employed as the contacts to polycrystalline MoS<sub>2</sub> films. Based on our analyses, only ~1.2 nm of ALD grown TiS<sub>x</sub> is sufficient for unleashing the most from the electrical capabilities of ALD-based MoS<sub>2</sub> FETs. Utilization of TiS<sub>x</sub> contacts improved the average ON-state device characteristics and led to the achievement of  $I_{\rm ON}$  as high as ~35  $\mu$ A  $\mu$ m<sup>-1</sup>. In addition and despite a higher Schottky barrier height, TiS<sub>x</sub> contacts reduced the  $R_c$  of the fabricated MoS<sub>2</sub> FETs down to ~5.0 MΩ  $\mu$ m, which is nearly a quarter of what was obtained for the bulk Ti contacts (21.4 MΩ  $\mu$ m).

# Data availability

The data that support the findings of this study are available from the corresponding author upon request.

# Conflicts of interest

The authors declare no competing financial interest.

# Acknowledgements

This work is funded by the European research council (ERC) under the grant Agreement No. 648787-ALDof2DTMDs. The authors would like to acknowledge the NanoLab TU/e for the cleanroom facilities as well as the technical support of E. J. Geluk, B. Krishnamoorthy, M. G. Dijstelbloem, P. P. Bax, T. de Vries, C. V. Helvoirt, J. J. A. Zeebregts and W. M. Dijkstra. Further, R. M. would like to express her special gratitude to Prof. Dr J. P. Hofmann and Y. Zhang from the laboratory of inorganic materials and catalysis (Department of Chemical Engineering and Chemistry, TU/e) for sulfurizing the MoO<sub>r</sub> samples in their home-built tube furnace, Dr S. B. Basuvalingam and J. J. P. M. Schulpen for scientific and practical discussions, M. A. Taheri (founder of Cosmointel Inc.) for graciously enabling access to T-consciousness fields used in this work, Molecular Materials and Nano-systems (M2N) research group (Department of Applied Physics, TU/e) for supplying resources to conduct the electrical measurements as well as SMART Photonics to provide access to their glove box for sample storage. A. A. S. would also like to thank NWO, The Netherlands, SERB (SERB/2017/1562) India, and SRMIST for the financial support and research funding.

### References

- 1 S. Manzeli, D. Ovchinnikov, D. Pasquier, O. V. Yazyev and A. Kis, *Nat. Rev. Mater.*, 2017, **2**, 17033.

- 2 M. Chhowalla, D. Jena and H. Zhang, *Nat. Rev. Mater.*, 2016, 1, 16052.

- 3 A. K. Geim and I. V Grigorieva, Nature, 2013, 499, 419-425.

- 4 R. Ganatra and Q. Zhang, ACS Nano, 2014, 8, 4074-4099.

- 5 B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti and A. Kis, *Nat. Nanotechnol.*, 2011, **6**, 147–150.

- 6 C. J. McClellan, E. Yalon, K. K. H. Smithe, S. V. Suryavanshi and E. Pop, *ACS Nano*, 2021, **15**, 1587–1596.

- 7 Y. Liu, J. Guo, Y. Wu, E. Zhu, N. O. Weiss, Q. He, H. Wu,

H. C. Cheng, Y. Xu, I. Shakir, Y. Huang and X. Duan, *Nano Lett.*, 2016, 16, 6337–6342.

- 8 P.-C. Shen, C. Su, Y. Lin, A.-S. Chou, C.-C. Cheng, J.-H. Park, M.-H. Chiu, A.-Y. Lu, H.-L. Tang, M. M. Tavakoli, G. Pitner, X. Ji, Z. Cai, N. Mao, J. Wang, V. Tung, J. Li, J. Bokor, A. Zettl, C.-I. Wu, T. Palacios, L.-J. Li and J. Kong, *Nature*, 2021, **593**, 211–217.

- 9 Y. Y. Illarionov, K. K. H. Smithe, M. Waltl, T. Knobloch, E. Pop and T. Grasser, *IEEE Electron Device Lett.*, 2017, **38**, 1763–1766.

- A. Leonhardt, D. Chiappe, V. V. Afanas'ev, S. El Kazzi, I. Shlyakhov, T. Conard, A. Franquet, C. Huyghebaert and S. de Gendt, ACS Appl. Mater. Interfaces, 2019, 11, 42697–42707.

- 11 W. Li, J. Zhou, S. Cai, Z. Yu, J. Zhang, N. Fang, T. Li, Y. Wu, T. Chen, X. Xie, H. Ma, K. Yan, N. Dai, X. Wu, H. Zhao, Z. Wang, D. He, L. Pan, Y. Shi, P. Wang, W. Chen, K. Nagashio, X. Duan and X. Wang, *Nat. Electron.*, 2019, 2, 563–571.

- 12 P. Bolshakov, C. M. Smyth, A. Khosravi, P. Zhao, P. K. Hurley, C. L. Hinkle, R. M. Wallace and C. D. Young, ACS Appl. Electron. Mater., 2019, 1, 210–219.

- 13 K. Kang, S. Xie, L. Huang, Y. Han, P. Y. Huang, K. F. Mak, C.-J. Kim, D. Muller and J. Park, *Nature*, 2015, **520**, 656–660.

- 14 S. Das, H.-Y. Chen, A. V. Penumatcha and J. Appenzeller, *Nano Lett.*, 2013, **13**, 100–105.

- 15 K. K. H. Smithe, S. V. Suryavanshi, M. Muñoz Rojo, A. D. Tedjarati and E. Pop, *ACS Nano*, 2017, **11**, 8456–8463.

- 16 B. Radisavljevic, M. B. Whitwick and A. Kis, *ACS Nano*, 2011, 5, 9934–9938.

- 17 S. Wachter, D. K. Polyushkin, O. Bethge and T. Mueller, *Nat. Commun.*, 2017, **8**, 14948.

- 18 C. Huyghebaert, T. Schram, Q. Smets, T. Kumar Agarwal, D. Verreck, S. Brems, A. Phommahaxay, D. Chiappe, S. El Kazzi, C. Lockhart de la Rosa, G. Arutchelvan, D. Cott, J. Ludwig, A. Gaur, S. Sutar, A. Leonhardt, D. Marinov, D. Lin, M. Caymax, I. Asselberghs, G. Pourtois and I. P. Radu, *IEEE International Electron Devices Meeting* (*IEDM*), 2018, DOI: 10.1109/IEDM.2018.8614679.

- 19 A. Afzalian, npj 2D Mater. Appl., 2021, 5, 5.

- 20 K. Alam and R. K. Lake, *IEEE Trans. Electron Devices*, 2012, 59, 3250–3254.

- 21 A. Allain, J. Kang, K. Banerjee and A. Kis, *Nat. Mater.*, 2015, 14, 1195–1205.

- 22 IEEE International Roadmap for Devices and Systems IEEE IRDS<sup>™</sup>, https://irds.ieee.org.

- 23 S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, John Wiley & Sons, Inc., Hoboken, NJ, USA, 2006.

- 24 Y. Taur and T. H. Ning, *Fundamentals of Modern VLSI Devices*, Cambridge University Press, 2009.

- 25 H.-J. Chuang, B. Chamlagain, M. Koehler, M. M. Perera, J. Yan, D. Mandrus, D. Tománek and Z. Zhou, *Nano Lett.*, 2016, 16, 1896–1902.

- 26 K. Heo, S.-H. Jo, J. Shim, D.-H. Kang, J.-H. Kim and J.-H. Park, *ACS Appl. Mater. Interfaces*, 2018, **10**, 32765–32772.

- 27 R. Kappera, D. Voiry, S. E. Yalcin, B. Branch, G. Gupta, A. D. Mohite and M. Chhowalla, *Nat. Mater.*, 2014, **13**, 1128–1134.

- 28 S. Lee, A. Tang, S. Aloni and H.-S. Philip Wong, *Nano Lett.*, 2016, **16**, 276–281.

- 29 W. Park, Y. Kim, S. K. Lee, U. Jung, J. Ho Yang, C. Cho, Y. Ji Kim, S. K. Lim, I. S. Hwang, H.-B.-R. Lee and B. H. Lee, 2014 IEEE International Electron Devices Meeting, 2014, DOI: 10.1109/IEDM.2014.7046986.

- 30 A. Alharbi and D. Shahrjerdi, *IEEE Trans. Electron Devices*, 2018, **65**, 4084–4092.

- 31 K. Parto, A. Pal, T. Chavan, K. Agashiwala, C.-H. Yeh, W. Cao and K. Banerjee, *Phys. Rev. Appl.*, 2021, **15**, 1–17.

- 32 M. H. D. Guimarães, H. Gao, Y. Han, K. Kang, S. Xie, C.-J. Kim, D. A. Muller, D. C. Ralph and J. Park, ACS Nano, 2016, **10**, 6392–6399.

- 33 X. Cui, G.-H. Lee, Y. D. Kim, G. Arefe, P. Y. Huang, C.-H. Lee, D. A. Chenet, X. Zhang, L. Wang, F. Ye, F. Pizzocchero, B. S. Jessen, K. Watanabe, T. Taniguchi, D. A. Muller, T. Low, P. Kim and J. Hone, *Nat. Nanotechnol.*, 2015, 10, 534–540.

- 34 W. S. Leong, Q. Ji, N. Mao, Y. Han, H. Wang, A. J. Goodman,

A. Vignon, C. Su, Y. Guo, P.-C. Shen, Z. Gao, D. A. Muller,

W. A. Tisdale and J. Kong, *J. Am. Chem. Soc.*, 2018, 140, 12354–12358.

- 35 Y. Liu, H. Wu, H. C. Cheng, S. Yang, E. Zhu, Q. He, M. Ding, D. Li, J. Guo, N. O. Weiss, Y. Huang and X. Duan, *Nano Lett.*, 2015, **15**, 3030–3034.

- 36 S. S. Chee, D. Seo, H. Kim, H. Jang, S. Lee, S. P. Moon, K. H. Lee, S. W. Kim, H. Choi and M. H. Ham, *Adv. Mater.*, 2019, **31**, 1–7.

- 37 W. S. Leong, X. Luo, Y. Li, K. H. Khoo, S. Y. Quek and J. T. L. Thong, ACS Nano, 2015, 9, 869–877.

- 38 Y. Du, L. Yang, J. Zhang, H. Liu, K. Majumdar, P. D. Kirsch and P. D. Ye, *IEEE Electron Device Lett.*, 2014, **35**, 599–601.

- 39 J. Li, X. Yang, Y. Liu, B. Huang, R. Wu, Z. Zhang, B. Zhao, H. Ma, W. Dang, Z. Wei, K. Wang, Z. Lin, X. Yan, M. Sun, B. Li, X. Pan, J. Luo, G. Zhang, Y. Liu, Y. Huang, X. Duan and X. Duan, *Nature*, 2020, **579**, 368–374.

- 40 H. Bark, Y. Choi, J. Jung, J. H. Kim, H. Kwon, J. Lee, Z. Lee, J. H. Cho and C. Lee, *Nanoscale*, 2018, **10**, 1056–1062.

- 41 J. Kang, W. Liu, D. Sarkar, D. Jena and K. Banerjee, *Phys. Rev. X*, 2014, **4**, 031005.

- 42 C. Gong, L. Colombo, R. M. Wallace and K. Cho, *Nano Lett.*, 2014, **14**, 1714–1720.

- 43 C. Kim, I. Moon, D. Lee, M. S. Choi, F. Ahmed, S. Nam,

Y. Cho, H.-J. Shin, S. Park and W. J. Yoo, *ACS Nano*, 2017,

11, 1588–1596.

- 44 M. Farmanbar and G. Brocks, *Adv. Electron. Mater.*, 2016, 2, 1500405.

- 45 Y. Liu, P. Stradins and S. H. Wei, Sci. Adv., 2016, 2, 1-7.

- 46 Y. J. Yu, Y. Zhao, S. Ryu, L. E. Brus, K. S. Kim and P. Kim, *Nano Lett.*, 2009, **9**, 3430-3434.

- 47 H. Ago, IEEE International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), 2020, DOI: 10.1109/ VLSI-TSA48913.2020.9203747.

- 48 Y.-H. Lee, X.-Q. Zhang, W. Zhang, M.-T. Chang, C.-T. Lin, K.-D. Chang, Y.-C. Yu, J. T.-W. Wang, C.-S. Chang, L.-J. Li and T.-W. Lin, *Adv. Mater.*, 2012, 24, 2320–2325.

- 49 D. Chiappe, J. Ludwig, A. Leonhardt, S. El Kazzi, A. Nalin Mehta, T. Nuytten, U. Celano, S. Sutar, G. Pourtois, M. Caymax, K. Paredis, W. Vandervorst, D. Lin, S. De Gendt, K. Barla, C. Huyghebaert, I. Asselberghs and I. Radu, *Nanotechnology*, 2018, **29**, 425602.

- 50 T. Kim, J. Mun, H. Park, D. Joung, M. Diware, C. Won, J. Park, S.-H. Jeong and S.-W. Kang, *Nanotechnology*, 2017, 28, 18LT01.

- 51 Y. Zhan, Z. Liu, S. Najmaei, P. M. Ajayan and J. Lou, *Small*, 2012, **8**, 966–971.

- 52 Z.-L. Tian, D.-H. Zhao, H. Liu, H. Zhu, L. Chen, Q.-Q. Sun and D. W. Zhang, ACS Appl. Nano Mater., 2019, 2, 7810–7818.

- 53 W. Jeon, Y. Cho, S. Jo, J. H. Ahn and S. J. Jeong, *Adv. Mater.*, 2017, **29**, 1–8.

- 54 J. J. Pyeon, I.-H. Baek, W. C. Lim, K. H. Chae, S. H. Han, G. Y. Lee, S.-H. Baek, J.-S. Kim, J.-W. Choi, T.-M. Chung, J. H. Han, C.-Y. Kang and S. K. Kim, *Nanoscale*, 2018, **10**, 17712–17721.

- 55 J.-G. Song, J. Park, W. Lee, T. Choi, H. Jung, C. W. Lee, S.-H. Hwang, J. M. Myoung, J.-H. Jung, S.-H. Kim, C. Lansalot-Matras and H. Kim, ACS Nano, 2013, 7, 11333– 11340.

- 56 S. B. Basuvalingam, M. A. Bloodgood, M. A. Verheijen, W. M. M. Kessels and A. A. Bol, ACS Appl. Nano Mater., 2021, 4, 514–521.

- 57 A. Sharma, R. Mahlouji, L. Wu, M. A. Verheijen, V. Vandalon,

S. Balasubramanyam, J. P. Hofmann, W. M. M. (Erwin)

Kessels and A. A. Bol, *Nanotechnology*, 2020, 31, 255603.

- 58 S. M. George, Chem. Rev., 2010, 110, 111-131.

- 59 H. B. Profijt, S. E. Potts, M. C. M. van de Sanden and W. M. M. Kessels, J. Vac. Sci. Technol., A, 2011, 29, 050801.

- 60 C. S. Cucinotta, K. Dolui, H. Pettersson, Q. M. Ramasse,

E. Long, S. E. O'Brian, V. Nicolosi and S. Sanvito, *J. Phys. Chem. C*, 2015, **119**, 15707–15715.

- 61 J. Gao and M. Gupta, npj 2D Mater. Appl., 2020, 4, 1-9.

- 62 T. Das, S. Chakraborty, R. Ahuja and G. P. Das, *ChemPhysChem*, 2019, **20**, 608–617.

- 63 G. Yin, H. Zhao, J. Feng, J. Sun, J. Yan, Z. Liu, S. Lin and S. (Frank) Liu, *J. Mater. Chem. A*, 2018, 6, 9132–9138.

- 64 M. F. J. Vos, B. Macco, N. F. W. Thissen, A. A. Bol and W. M. M. (Erwin) Kessels, *J. Vac. Sci. Technol.*, A, 2016, 34, 01A103.

- 65 R. Mahlouji, M. A. Verheijen, Y. Zhang, J. P. Hofmann,

W. M. M. Kessels and A. A. Bol, *Adv. Electron. Mater.*, 2022,

8, 2100781.

- 66 S. B. Basuvalingam, Y. Zhang, M. A. Bloodgood, R. H. Godiksen, A. G. Curto, J. P. Hofmann, M. A. Verheijen, W. M. M. Kessels and A. A. Bol, *Chem. Mater.*, 2019, **31**, 9354–9362.

- R. Mahlouji, Y. Zhang, M. A. Verheijen, J. P. Hofmann,

W. M. M. Kessels, A. A. Sagade and A. A. Bol, *ACS Appl. Electron. Mater.*, 2021, 3, 3185–3199.

- 68 K. B. Jinesh, J. L. van Hemmen, M. C. M. van de Sanden,

F. Roozeboom, J. H. Klootwijk, W. F. A. Besling and

W. M. M. Kessels, *J. Electrochem. Soc.*, 2011, 158, G21.

- 69 A. Sharma, V. Longo, M. A. Verheijen, A. A. Bol and W. M. M. (Erwin) Kessels, *J. Vac. Sci. Technol.*, A, 2017, 35, 01B130.

- 70 K. Schauble, D. Zakhidov, E. Yalon, S. Deshmukh,

R. W. Grady, K. A. Cooley, C. J. McClellan, S. Vaziri,

D. Passarello, S. E. Mohney, M. F. Toney, A. K. Sood,

A. Salleo and E. Pop, *ACS Nano*, 2020, 14, 14798–14808.

- 71 Y. Kim, A. R. Kim, J. H. Yang, K. E. Chang, J.-D. Kwon, S. Y. Choi, J. Park, K. E. Lee, D.-H. Kim, S. M. Choi, K. H. Lee, B. H. Lee, M. G. Hahm and B. Cho, *Nano Lett.*, 2016, **16**, 5928–5933.

- 72 S. Das and J. Appenzeller, Nano Lett., 2013, 13, 3396-3402.

- 73 S. Das and J. Appenzeller, *Phys. Status Solidi RRL*, 2013, 7, 268–273.

- 74 D. K. Schroder, *Semiconductor Material and Device Characterization*, John Wiley & Sons, Inc., Hoboken, NJ, USA, 2005.

- 75 S. B. Mitta, M. S. Choi, A. Nipane, F. Ali, C. Kim, J. T. Teherani, J. Hone and W. J. Yoo, *2D Mater.*, 2021, **8**, 012002.

- 76 I. Miccoli, F. Edler, H. Pfnür and C. Tegenkamp, J. Phys.: Condens. Matter, 2015, 27, 223201.

- 77 H. Park, J. Lee, C.-J. Lee, J. Kang, J. Yun, H. Noh, M. Park, J. Lee, Y. Park, J. Park, M. Choi, S. Lee and H. Park, *Nanomaterials*, 2022, **12**, 206.

- 78 S. Y. Min, C. Cho, G. W. Shim, I.-J. Park, D. Y. Jung, Y. Woo, J.-Y. Lee and S.-Y. Choi, *FlatChem*, 2018, 7, 19–25.

- 79 A. Anwar, B. Nabet, J. Culp and F. Castro, *J. Appl. Phys.*, 1999, **85**, 2663–2666.

- 80 K. Cho, J. Pak, J.-K. Kim, K. Kang, T.-Y. Kim, J. Shin, B. Y. Choi, S. Chung and T. Lee, *Adv. Mater.*, 2018, 30, 1705540.

- 81 J.-R. Chen, P. M. Odenthal, A. G. Swartz, G. C. Floyd, H. Wen, K. Y. Luo and R. K. Kawakami, *Nano Lett.*, 2013, 13, 3106– 3110.