# Nanoscale Advances

# **REVIEW**

View Article Online

View Journal | View Issue

Cite this: Nanoscale Adv., 2024, 6,

# Challenges and opportunities in engineering nextgeneration 3D microelectronic devices: improved performance and higher integration density

Niharika Singh, <sup>a</sup> Kingshuk Srivastava, <sup>\*b</sup> Ajay Kumar, <sup>c</sup> Neha Yadav, <sup>d</sup> Ashish Yadav, <sup>b</sup> \*d Santosh Dubey, <sup>b</sup> <sup>k</sup> Rajesh Singh, <sup>ef</sup> Anita Gehlot, <sup>ef</sup> Ajay Singh Verma, <sup>g</sup> Neha Gupta, <sup>h</sup> Tanuj Kumar, <sup>b</sup> <sup>i</sup> Yongling Wu, <sup>d</sup> <sup>d</sup> Zheng Hongyu, <sup>d</sup> Aniruddha Mondal, <sup>j</sup> Kailash Pandey, <sup>k</sup> Ranjeet Brajpuriya, <sup>k</sup> Shalendra Kumar <sup>b</sup> <sup>k</sup> and Rajeev Gupta\*

In recent years, nanotechnology and materials science have evolved and matured, making it increasingly easier to design and fabricate next-generation 3D microelectronics. The process has changed drastically from traditional 2D microelectronics, resulting in improved performance, higher integration density, and new functionalities. As applications become more complex and power-intensive, this technology can address the demands of high-performance computing, advanced sensors, and cutting-edge communication systems *via* wearable, flexible devices, *etc.* To manufacture higher-density microelectronics, recent advances in the fabrication of such 3D devices are discussed. Furthermore, the paper stresses the importance of novel materials and architectures, such as monolithic 3D integration and heterogeneous integration, in overcoming these challenges. We emphasize the importance of addressing complex issues to achieve better performance and higher integration density, which will play an important role in shaping the next generation of microelectronic devices. The multifaceted challenges involved in developing next-generation 3D microelectronic devices are also highlighted.

Received 14th July 2024 Accepted 29th July 2024

DOI: 10.1039/d4na00578c

rsc.li/nanoscale-advances

## 1 Introduction

Miniaturized three-dimensional (3D) microelectronic devices made of advanced materials are expected to significantly impact various consumer and military applications in the near future. <sup>1-3</sup> These include energy storage/harvesting, photonic

sensing, wearable electronics, biomedical technologies, 4,5 micro/nanoelectromechanical systems (MEMS/NEMS),6,7 and high-performance transistors, to name a few.8,9 For example, the currently used structure of Fin-FETs (tri-gate) transistors, which evolved from the traditional planar design, needs to advance further towards structures with gate-all-around (GAA) in 3D.10-12 Using such advanced 3D structures enables higher functional density, higher performance, and less power consumption.13,14 New R&D innovations in 3D transistors through advanced manufacturing and processing technologies is believed to enrich the future microelectronics industry.15-18 Another illustration is the demand for nextgeneration chips and dense integrated circuits (ICs), which are required to perform a wider range of functions more extensively.19 This is especially desired beyond the technologies currently achievable through a simple lithography scaling method based on a single chip (system-on-chip).20,21 To this end, researchers and engineers are working on technologies dealing with heterogeneous integrations in 3D architecture, including 3D IC packaging, 3D IC integration, and 3D Si integration.<sup>22,23</sup> 3D IC integration is considered superior to 3D IC packaging as it allows stacking of much thinner IC chips with through-silicon-via (TSV) technology and micro-bumps. This architecture enables energy-efficient technology that

<sup>&</sup>lt;sup>a</sup>Department of Informatics, School of Computer Science, University of Petroleum & Energy Studies, Dehradun-248007, Uttarakhand, India

<sup>&</sup>lt;sup>b</sup>Department of CSE, Vivekananda Global University, Jaipur, Rajasthan, 303012, India. E-mail: kingshuk.india@gmail.com

<sup>&#</sup>x27;Jaypee Institute of Information Technology, Noida, Uttar Pradesh, India

<sup>&</sup>lt;sup>d</sup>Center for Advanced Laser Manufacturing (CALM), Shandong University of Technology, Zibo, 255000, P. R. China. E-mail: ashish84yadav@gmail.com

<sup>&</sup>lt;sup>e</sup>Uttaranchal Institute of Technology, Uttaranchal University, Dehradun 248007, India <sup>†</sup>Department of Project Management, Universidad Internacional Iberoamericana, Campeche 24560, CP, Mexico

<sup>&</sup>lt;sup>8</sup>Division of Research and Innovation, School of Applied and Life Sciences, Uttaranchal University, Dehradun, Uttarakhand, 248007, India

<sup>&</sup>lt;sup>h</sup>Applied Science Department, Greater Noida Institute of Technology, Greater Noida, 201310. India

Department of Nanoscience & Materials, Central University of Jammu, Jammu, 181143, India

Department of Physics, National Institute of Technology Durgapur, Durgapur, 713209, West Bengal, India

<sup>\*</sup>Department of Physics, School of Engineering, University of Petroleum & Energy Studies, Dehradun 248007, Uttarakhand, India. E-mail: rajeev@ddn.upes.ac.in

offers higher integration, covers small areas, and performs better.<sup>24</sup>

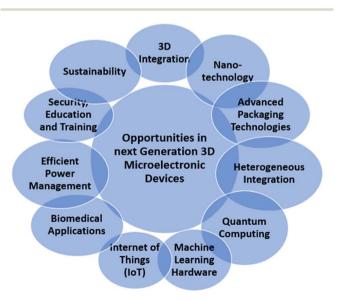

These numerous advantages of 3D devices and systems are poised to drive the development of next-generation microelectronics and photonics25-27 and offer superior benefits: light weight, enhanced functional performance, energy efficiency, a smaller footprint, and cost-effectiveness compared to the existing planar 2D devices. 28,29 3D microelectronic devices also offer a high degree of integration and productivity. 30,31 Despite the advances that have been made, critical manufacturing technical challenges remain to be solved, especially in batch manufacturing, including thermal management, via formation, and thin-wafer handling.30,32 In addition, devices with more complex 3D geometries, including conical spirals and hemispherical and polyhedral shapes, would be needed in future technologies.33-35 These complex 3D architectures require advanced manufacturing processes for optimum performance.36,37 Quantum computing is still in its infancy and is an exciting area within 3D microelectronics (Fig. 1).38-40

Engineers are working on developing the hardware components and architectures required for quantum computers, which have the potential to revolutionize computing. 3D microelectronic devices, including implantable devices, diagnostics, and drug delivery systems, have significant medical potential.41-43 The Internet of Things (IoT) relies on small, lowpower devices that can be integrated into everyday objects. Engineers can work on developing 3D microelectronics that meet the stringent requirements of IoT applications, such as size, low power consumption, and wireless connectivity.44-46 With the growing demand for machine learning and artificial intelligence, there are opportunities to design specialized hardware for these applications. This can include neuromorphic computing and specialized accelerators.47-49 As with all technological advancements,

Fig. 1 Next-generation 3D microelectronic devices are evolving rapidly, offering numerous opportunities in various industries.

sustainability is an important consideration. Engineers are looking forward to developing a new eco-friendly class that can work on developing eco-friendly materials and manufacturing processes to reduce the environmental impact of 3D microelectronics. 47,48,50–52 With the increasing connectivity of devices, security is a paramount concern. Engineers and researchers in this field play a crucial role in shaping the future of electronics, computing, and many other industries. 53,54 Several fabrication steps and intricate designs are involved in 3D microelectronic devices, which are smaller, faster, more powerful, and more energy-efficient than conventional electronics. 55,56

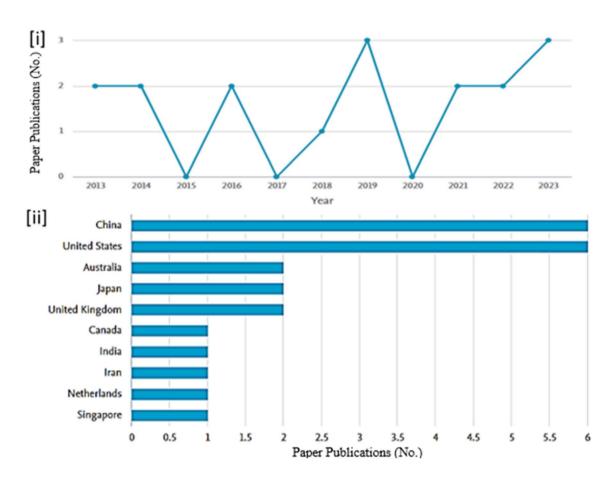

Fig. 2 is significant to researchers, industry experts, and decision-makers alike, encouraging collaboration and accelerating progress in next-generation 3D microelectronic devices. The increasing number of publications on these devices year by year and country by country demonstrates their importance. The next generation of 3D microelectronic devices could revolutionize a wide range of industrial areas. Engineers and researchers in this field play a crucial role in shaping the future of electronics, computing, and many other industries.

Several new materials have emerged and gained attention in 3D microelectronic devices. These materials are unique in their ability to meet semiconductor technology demands.<sup>57,58</sup> A glimpse of the state-of-the-art materials is given as follows:

- (1) Ultra-low dielectric constants can reduce signal propagation delays and crosstalk in high-speed interconnects. Research is being conducted on organosilicates (SiCOH), porous silica, and organic polymers.

- (2) A high-k dielectric has replaced silicon dioxide gate insulators in advanced transistors, allowing further device scaling and improved electrostatic control. For high-k gate dielectrics, hafnium oxide (HfO<sub>2</sub>) and zirconium oxide (ZrO<sub>2</sub>) are being investigated.

- (3) Semiconductors made of InP and GaN have superior electron mobility. High-frequency and high-power applications use silicon-based platforms.

- (4) Because of their nanoscale thickness, two-dimensional (2D) materials like graphene and TMDs have unique electronic and optical properties. Sensors, transistors, and interconnects are being investigated to enhance performance, increase flexibility, and save energy.

- (5) Chalcogenide compounds (*e.g.*, GeSbTe) are commonly used as phase change materials (PCMs) in non-volatile memories (PCMs). Due to reversible phase transitions, PCMs are ideal for non-volatile storage and high-speed switching.

- (6) MOFs are porous materials composed of metal ions or clusters connected by organic ligands. Microelectronic devices are used for gas sensing, catalysis, and energy storage because of their high surface area, tunable pore size, and varied functionality.

- (7) Flexible substrates, such as polyimide and PET, are required for wearable electronic devices. These materials allow electronic components to be integrated into flexible or curved surfaces in healthcare and consumer electronics.

Fig. 2 Research papers published on next-generation 3D microelectronic devices [i] year-wise, [ii] country-wise and [iii] area-wise.

Advanced Materials & Advanced Packaging Through-Silicon **Technologies** Via (TSV) Die-Stacking Technology and Package on-Package Thin-Film Assembly Transistor (TFT) Manufacturing Technology technologies to create 3D microelectronic devices Monolithic 3D Integration Wafer-on-Wafer Bonding **3D Printing** Micro-Electro-Mechanical Systems (MEMS)

Fig. 3 Various manufacturing technologies for developing 3E microelectronic devices.

Technology

Researchers are developing these materials to enhance the efficiency, performance, and functionality of microelectronic devices across a wide range of applications.

# 2 Manufacturing technologies for developing 3D microelectronic devices

Researchers have shown various manufacturing methods for 3D microelectronic devices comprising different structural and functional features.<sup>32,59</sup> Various manufacturing technologies are used to manufacture 3D microelectronic devices [Fig. 3].

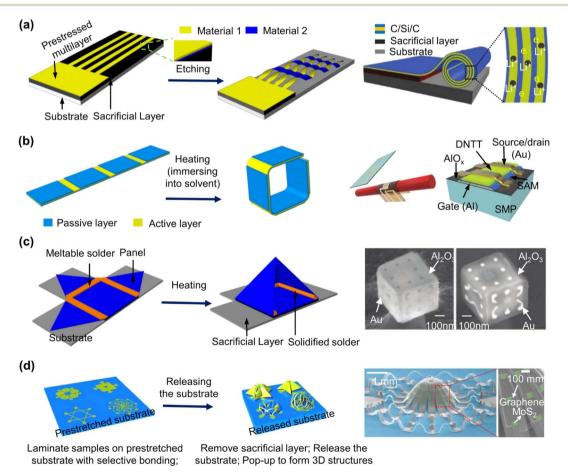

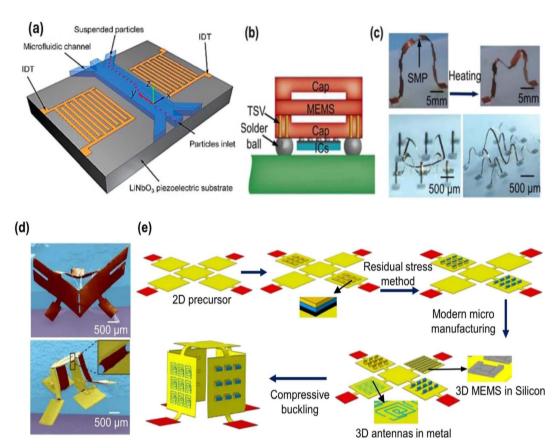

These manufacturing methods mainly include micromanufacturing and machining, mechanically guided 3D assembly approaches, and self-assembly processes. New techniques that include hybrid strategies are also being explored.59-61 3D microelectronic structures featuring simple designs yield suspended and stacked components that can be fabricated relatively directly through modern manufacturing technologies, including lithographic patterning, etching, and deposition. 62-64 On the other hand, methods based on mechanically guided 3D assembly can be employed as mature planar processing techniques available in the semiconductor industries to fabricate 2D precursor structures. 65-68 These 2D structures are subsequently processed into well-defined 3D forms by leveraging mechanically guided forces, including capillary forces, residual stresses, and constraint forces on inactive materials.<sup>69,70</sup> Many possibilities remain for improving and expanding existing manufacturing technologies.71 For example, futuristic manufacturing will aim to develop a universal method for deterministically controlling and forming 3D microelectronic devices with very high geometric complexity and ultra-small-scale precision. 32,72,73

In recent years, several fields, including semiconductors, have rapidly advanced in 3D and heterogeneous integration. This involves various techniques such as through-silicon via (TSV) interposer-based integration, fan-out wafer-level packaging (FOWLP), chip-on-chip, system-on-package (SoP), 2.5D and 3D circuits, monolithic 3D integration, and wafer-to-wafer bonding.<sup>74,75</sup> The TSV approach stacks multiple silicon wafers vertically with vertical interconnects running through the silicon substrate, resulting in shorter interconnects, smaller footprints, and better performance. Silicon substrates with high-density interconnects act as interposers, combining different semiconductor components like memory, logic, and sensors into one package. FOWLP allows the incorporation of multiple chips into a single package by redistributing the connection points, achieving size reduction, increased input/ output density, and improved electrical performance.76

Chips are stacked on each other, often using TSVs or micro bumps to connect them. CoC integration integrates logic and memory. Multichip SoPs include processors, memory, and sensors together in one package. The result is a highly integrated system that is highly efficient and performs well. The 2.5D and 3D IC integration approaches involve stacking multiple dies or wafers with interconnects. Die connections are made using interposers in 2.5D ICs, while multiple dies are stacked directly in 3D ICs. To ICs, while multiple dies are stacked directly in 3D ICs. In monolithic 3D integration, heterogeneous components are densely integrated with vertical connectivity. Multi-die integration is accomplished through W2W bonding, using TSVs or micro bumps to link multiple wafers vertically.

This integration structure and approach are continuously improving, becoming more compact, and enabling new capabilities in computing, networking, automotive, and consumer electronics.

# 2.1 Manufacturing routes involving micromachining processes

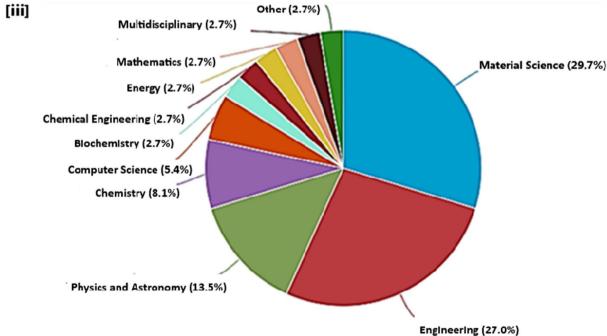

Various micro-manufacturing technologies employing topdown and bottom-up micromachining approaches, including selective etching, photoresist, wire bonding, and thinning processes, are shown in Fig. 4. In the microelectronics industry, several micromachining technologies have been employed, including laser and focused ion beam machining, deep reactive ion etching (DRIE), hot embossing, and bulk/surface micromachining.88,89 Bulk or surface micromachining and DRIE methods have attracted much attention and are widely used in microelectronics industries.90 Selective removal of the substrate material by chemical or physical means involves bulk micromachining to obtain 3D components.91,92 In contrast, surface micromachining techniques can achieve more precise dimensional and structural control.93 These techniques involve stepby-step deposition and patterning of sacrificial and structural layers, followed by the selective removal of the underlying sacrificial layer.24

The researchers initially developed a top-down approach for building 3D MEMS devices. DRIE was employed to fabricate 3D MEMS with high aspect-ratio features.<sup>94,95</sup> This was achieved by

Fig. 4 (a) A schematic presentation shows a top-down 3D cantilever fabrication enabled by the etching of the sacrificial layer and a corresponding SEM image of a 3D MEMS mirror.<sup>80</sup> (b) Fabrication of nanowire 'NW' resonator arrays by a bottom-up integration process.<sup>81</sup> (c and d) Schematic illustrations showing the fabrication process and a corresponding SEM image of 3D stacked gate-all-around 'GAA' transistors. GAA transistors are fabricated by selective etching of sacrificial layers and alternating etching-passivation steps [reproduced with permission from ref. 82. Copyright, Elsevier, 2020]. (e–g) 3D integration technology (three types) is displayed along with representative images.<sup>83</sup> (e) Stacked-die with wire bonding and package-on-package stacking, (f) memory stacking with through-silicon-via 'TSVs' [reproduced with permission from ref. 84. Copyright, Elsevier, 2020] and (g) wafer-to-wafer bonding<sup>85</sup> [reproduced with permission from ref. 86. Copyright, Elsevier, 2011].<sup>87</sup>

chipwork

alternately etching Si and depositing etch-resistant material on the sidewalls. This technique is considered a cost-effective process that offers precision and can be extended to different materials, including silicon carbide, titanium, tungsten, glass, and polymers.<sup>96,97</sup> Furthermore, it has been shown that for manufacturing 3D MEMS with diverse suspension geometries,

10 µm

n+ InP

a viable approach is to combine various micromachining technologies to utilize the features of each technology.24

On the other hand, building smaller units involving atoms and molecules into more complex assemblies based on their properties needs bottom-up micromachining approaches.98-100 This also represents a well-known manufacturing approach for self-assembling various morphological functional nanomaterials. Researchers have demonstrated combining bottom-up nanomaterials with micromachining technologies as an effective integration that can facilitate the fabrication of 3D nanodevices. 101-103 These bottom-up integration processes were employed to fabricate nanowire 'NW' resonator arrays. 104,105

Microgeneration technologies aid in efficiently managing energy resources, which is essential for a long-term future 106. Variable design control compensates for the frameworks' restrictions by employing switches based on current utilization and energy supply accessibility.107 A tiny battery capacity crossover energy arrangement is introduced. Using the collective energy of frameworks to meet electrical demands, reducing the dependence on the adjacent electricity company is possible. 108,109 Three alternative ways to control the system were compared, and the nonlinear reversal-based control scheme performed admirably. 3D microelectronic devices with highly varied structural and functional properties have led to the development of many manufacturing methods. 32 Recent studies have extended this discovery to a broader range of materials (such as silicon carbide, titanium, tungsten, glass, and polymers), demonstrating a cost-effective method for deep drawing with excellent selectivity and accuracy. 110,111 The tension between the top and base layers, controlled by the substantial manufacturing boundaries, promotes the self-movement of 2D structures into deterministic 3D designs after the specific scratching of the sacrificial layer. 112-115 The framed devices could include several 3D practical pieces across various length scales to coordinate several functionalities into a single framework.112-115

Rechargeable micro-batteries are critical power sources for microelectronic devices. 116,117 Two crucial goals for such devices are high energy output and a minimal footprint. Device configurations are crucial for improving output energy and reducing footprint size. We examine the progress made in

Fig. 5 (a) Schematic presentation of an application to lithium-ion batteries due to residual stress-induced rolling [reproduced with permission from ref. 132. Copyright, Wiley 2013]. (b) An application in 3D deployable organic thin-film transistors (OTFTs) fabricated by the foldingdominated method (reproduced with permission from ref. 133. Copyright, Wiley 2014). (c) An example of a representative microelectronic device with optically active split-ring resonator (SRRs) patterns is made by the induced folding-dominated method (reproduced with permission from ref. 134. Copyright, Wiley 2011]. (d) 3D photodetection systems that are capable of measuring incident light parameters developed by mechanically guided 3D assembly induced by compressive forces and a pre-strained substrate. 85,87,135

Nanoscale Advances Review

folded-up nanotechnology, a descendant of origami technology, in manufacturing micro-batteries. 118 On-chip electronic devices can readily incorporate three-dimensional sandwiched rMBs. The thickness of the electrode materials and the rMB's output energy are limited due to the sandwiched structure. 119 The energy density can be enhanced by transitioning from a sandwich to an interdigital architecture. 120,121 A common packaging option is to deposit polymer flexible and wearable substrates. Solid-state electrolytes, such as LiPON, can overcome the leakage problem, but their electrical conductivity is low, limiting the ability of rMBs to store energy. On the other hand, polymer-based electrolytes can achieve a good balance between high conductivity and operational stability.122,123

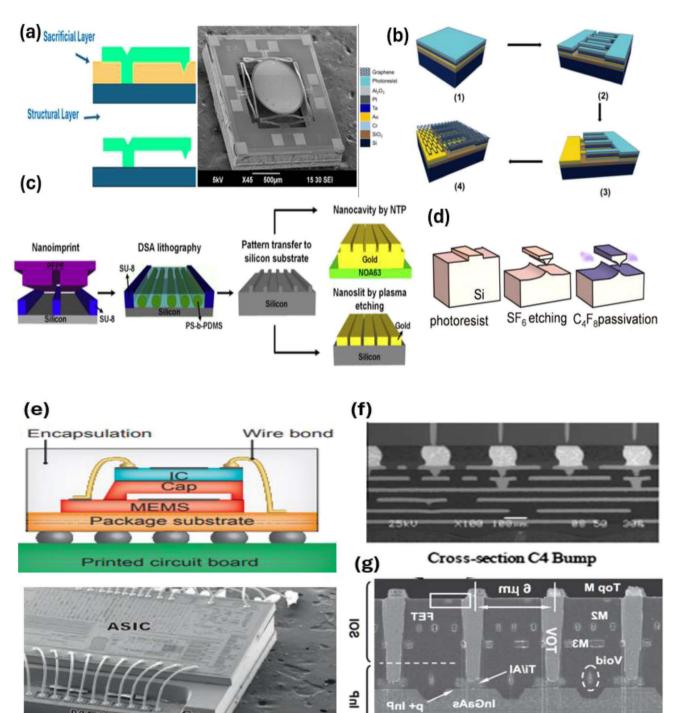

## 2.2 Mechanically guided 3D microelectronics assembly

Mechanically assisted manufacturing is a different method for creating 3D microelectronic devices capable of constructing complicated 3D geometries. 124-126 This method can be used to create multilayer and even hierarchical architectures. It can be used on various materials, including semiconductors, metals, polymers, and ceramics, and at various length scales, from tens of nanometers to centimeters. It is compatible with the semiconductor and integrated photonic industries. 127,128

The main characteristic of mechanically guided 3D assembly is different mechanical forces, including compressive forces due to a soft substrate, capillary forces, residual stress, and constraint forces (heat-, light-, and solvent-responsive active materials).129 This technology's main step is deliberately distorting 2D precursor structures into 3D shapes. The main methods for accomplishing this include bending, twisting, or a combination of both. 130,131 Several mechanically guided 3D microelectronic assembly procedures are schematically illustrated in Fig. 5, along with a few manufactured 3D devices. The steps involve a residual stress method used to fabricate characteristic tubular or helical 3D electronic devices at an ultrasmall scale. 136,137 Subsequently, the self-rolling of 2D precursors results in the deterministic 3D structures obtained after the sacrificial layer's selective etching. 129 Researchers have demonstrated several 3D electronic device prototypes using mechanically guided assembly. 138,139 The 3D devices that were fabricated include rolled-up field-effect transistors, 3D tubular infrared photodetectors with a widened visual field, and 3D radio frequency (RF)/microwave air-core transformers with enhanced performance compared to their on-chip counterparts. 140-142 Despite the advancements, it is important to note that the challenge of achieving the heterogeneous integration of multiple electronic components (e.g., ICs) at different in-plane locations remains.143

Daniel Karnaushenko et al.144 discussed modern microelectronic systems and their components as predominantly threedimensional (3D) devices that have decreased in size and weight to increase performance and reduce costs. Microelectronics has changed dramatically during the previous halfcentury in components and fully integrated systems. The rising compatibility defines the commencement of fully parallel waferscale production of 3D self-assembled microelectronic systems

among multiple technologies and innovative materials. 145,146 Deviations and inaccuracies in the structure and design continue to pose challenges that affect device yield. They can only be overcome by fine-tuning material characteristics and manufacturing methods, which will undoubtedly incorporate self-stabilizing technologies. 147-149 Although 3D self-assembled microelectronics is still in its early stages, powerful prototype devices have already paved the road for integration into commercially accessible microelectronic systems and used in real-world applications. 150-152 System-on-Package (SoP) technology based on silicon carriers can support robust chip manufacturing with high-yield/low-cost chips for various products of two- and three-dimensional product applications. 153 It can also provide modular design flexibility and high-performance integration of heterogeneous chip technologies. 154-156 The silicon carrier package's thermal expansion matches that of the chip, ensuring dependability even when the high-density chip micro-bump interconnections shrink in size. 157,158 This method appears to scale with semiconductor advancements in electrical, thermal, and I/O scaling.159 It will also assist in directing technology toward product applications that demonstrate the highest cost-effectiveness. The integration of silicon and packaging using new 2D and 3D structures is fascinating for supporting system requirements and new volume-based product applications. 160-162

## 2.3 Compact 3D self-assembled microelectronics

A new area of research, 3D self-assembled microelectronic devices, is anticipated to simplify production procedures and offer unique functions in the microelectronics industry of the future. 163,164 Creating sophisticated 3D architectures from initially planar membranes is quickly becoming possible, which is a very effective method for producing 3D electronics. 165,166 Because it presents new prospects to integrate thin-film microelectronic functions in systems and devices with increased performance and higher integration density, 3D selfassembly has demonstrated its significant advantage in recent research. To optimize self-assembled 3D architectures, researchers have worked on resolving chemistry, structural stability, and yield problems and devising novel techniques. 167,168 Different 3D structures have been created using self-assembly techniques. Complex thin-film electrode architectures, 3D self-assembled passive and active components, as well as sensor, mechanical, and energy supply devices have all been successfully integrated (Fig. 6).144

The underlying mechanism of 3D self-assembly works parallelly, taking advantage of surface tension, extrinsic forces, and intrinsic interfacial and volumetric stresses. 169-171 For example, it has been shown that in the case of reorienting conventional MEMS and NEMS structures, positioning microelectronic components, and fabricating polyhedral architectures, the surface tension of various materials in the liquid phase plays a crucial role and has been extensively utilized.30 Similarly, extrinsic forces can be leveraged for structural buckling, which was utilized to form diverse pop-up 3D architectures. 172 In another example, rolled-up tubular and

Mechanical Actuator **Passive** Switch Transformer Electrodes Inductor Interconnects Resonator, Antenna Resistor, Capacitor Active LED Diode Extrinsic guidance and **TFT Circuit** structural buckling Non-Linear Junctions **Polyhedral** Energy Photovoltaic

Fig. 6 Schematic illustrations show three distinct driving mechanisms; surface tension, extrinsic forces, and intrinsic interfacial and volumetric stresses that can be leveraged to fabricate 3D self-assembled microelectronic devices wafer-scale-processable and deployable. 144

Surface Tension

architectures were created by applying intrinsic interfacial or volumetric stresses.173,174

Microelectronics that are self-assembled have several intriguing possibilities. The most critical component is the 3D shape's compactness, which immediately enhances the form factor. 175 As a result, energy storage components like batteries, capacitors, and inductors perform better per footprint area. This has also been demonstrated to offer novel properties for magnetic sensors missing from the initial planar state. 176,177 According to research, 3D optical and electrical devices are employed as mechanical scaffolds to examine, work with, and interact with biological fluids and soft tissues.178 3D selfassembled microelectronics is still a nascent and developing field. But it is anticipated that potent prototype devices which have already been revealed could open the door to the microelectronics commercialization industry useful applications.144

2.3.1 Hybrid manufacturing technologies to realize 3D multifunctional microelectronics. Recent research suggests that combining various technologies can circumvent some technological constraints imposed by micro-manufacturing and self-assembly approaches. 61,179 For instance, scientists have used 3D IC integration technology to create an interposer (carrier) micro-device. For thermal control, this microdevice integrates fluidic microchannels made using wet etching (Fig. 7). The development of TSV-based 3D integration for the chip-scale package of MEMS and ICs was demonstrated using micromachining technology. 183,184 From an industrial standpoint, the heterogeneous integration of many functional components, such as logic processors, RF devices, biochips,

sensors, and MEMS, into a single chip can be revolutionary in providing affordable and value-added system solutions. 185,186

Thermoelectric Chem Source

Storage

Advanced 3D microelectronic packaging technology is currently very useful in meeting the requirements of portable electronics and heterogeneous integration roadmaps due to its ultra-thin and ultra-light design, good performance, and low power consumption.187,188 Another significant benefit is that it adheres to Moore's law at a much cheaper cost compared to the semiconductor industry. 189,190 Various facets of 3D packaging have also been investigated, including manufacturing, assembly, cost, design, modeling, heat management, material, etc. 191,192 Three-dimensional hyper integration is a revolutionary technique for building highly integrated micro-nano systems by vertically stacking and connecting numerous materials, technologies, and functional components. 193,194 Memory, handheld devices, and high-performance computers will lead to high-density multifunctional heterogeneous integration of InfoTech, NanoTech-BioTech systems. 195,196 The government, public, and private investors have invested heavily in developing stacked 3D silicon for years. This technology is mass-produced and stacked with 3D silicon components, and product designers can use foundry services. Stacked 3D silicon has already made a big difference in the microelectronics systems and products in which it is used. 197,198 Due to the presence of multiple gates, multi-gate FETs are a better option than planar MOSFETs for drain potential screening from channel. 110 FinFET devices have reduced fringing capacitances but that come with higher fabrication costs.199-201 They consume less power, are immune to SCEs, take up less space, and function faster.202 The most recent advancements in FinFET technology are examined

Fig. 7 Formation of 3D multifunctional microelectronics devices by hybrid manufacturing/assembly methods.<sup>217</sup> (a) Schematic illustration showing an interposer (carrier) device with fluidic microchannels for thermal management.<sup>180</sup> (b) Chip-scale integrated MEMS and ICs.<sup>213</sup> (c) Mechanically guided 3D assembly assisted by residual stresses [reproduced with permission from ref. 181. Copyright, Wiley 2017]. (d) The combination of mechanically guided 3D assembly and residual plastic deformations of metals results in freestanding 3D structures.<sup>182</sup> (e) Merging of micro-manufacturing technologies and other mechanically guided 3D assembly methods with 3D assembly based on compressive buckling.<sup>215</sup>

by addressing circuit and manufacturing issues and different FinFET structures, such as SOI MOSFETs and SOI NERFETS.<sup>202</sup>

New wireless technologies, including new usage patterns and protocols, transform our daily lives.203,204 The heterogeneous functionality required for expanding consumer, communication, and defense microsystems cannot be combined into a platform based on semiconductor device scaling because the convergence of communication, computing, optical, and sensing technologies necessitates complete system implementation on ultra-small form factor mobile platforms.205 It is possible to increase system-level performance, reduce form-factor, and lower power dissipation by utilizing 3D integration of low-power, highly efficient, process-optimized IC and packaging technologies. 205,206 The desire for multifunction mobile platform-based designs drives the demand for 3D integration of heterogeneous technologies. Monolithic 3D-ICs, stacked 3DICs, and POPs only make up a minor portion of a platform's overall system.207,208 The multifunction system must be reduced before the full advantages of 3D integration can be realized. Although there are significant challenges associated with 3D integration for wireless mobile internet and computer platforms, it also creates new

opportunities for system architecture, design, integration, manufacturing, and testing.209-211 Electronic connection and packing chores are typically carried out in 2D. To further miniaturize and enhance the functionality of electronic devices, 3D integration is required. 212,213 The desire for multifunction mobile platform-based designs drives the demand for 3D integration of heterogeneous technologies. With its ultra-thin and ultra-light design, and excellent performance while consuming very little power, advanced 3D microelectronic packaging technology is currently beneficial in achieving the demands of portable electronics and heterogeneous integration roadmaps.214 It adheres to Moore's law at a much lower cost compared to the semiconductor industry, which is another noteworthy advantage. Many other aspects of 3D packaging were explored, including fabrication, assembly, cost, design, modeling, heat management, material, and many more. 215,216

A mechanical-materials-and-reliability engineer will probably have to deal with problems related to exciting developing technologies in numerous fields. <sup>215,216</sup> Unless something unexpected disrupts the current trend and defines the near future, predicting future technology is not as difficult as it initially appears. This happens due to the sudden change in momentum

Heat dissipation Through-Silicon Via (TSV) Technology Thin Film Deposition and Uniformity Alignment and Registration Complex Process Flows Challenges and **Design Complexity** constraints in **Material Compatibility** fabrication of 3D **Process Variability** Microelectronic Testing and Reliability Devices Integration of Heterogeneous Components **Environmental and Sustainability Concerns Process Control and Monitoring** Scaling and Miniaturization

Standardization

Fig. 8 Various challenges and constraints in the fabrication of 3D Microelectronic Devices.

of these movements. Continuous innovation is required to meet the future demands of electrical and photonic technologies.<sup>214</sup> The fundamental problem is that silicon chips have limitations when it comes to integrating photonic capabilities, even though they enable our CPUs, computer memory, communication processors, and image sensors.217-219 Hence, a layer is used to construct optical waveguides to overcome this challenge and integrate photonics into bulk silicon complementary metaloxide-semiconductor devices. 220,221 This transistor-based photonic device can achieve many of the multi-chip approach's objectives when decoupled.

# Challenges and constraints in the fabrication of 3D microelectronic devices

Numerous constraints and challenges are associated with the fabrication of 3D microelectronic devices. 209,210 The following are some of the most important challenges and constraints in fabricating 3D microelectronic devices [Fig. 8].

Due to the increased power density and limited thermal dissipation in compact, multilayered structures, 3D microelectronic devices pose significant challenges in heat management. Variations in thermal expansion among materials can lead to stress, delamination, cracking, or warping. Unmanaged hotspots from active components can degrade overall performance, while temperature fluctuations impact device reliability due to mechanical stress from large gradients. Moreover, issues such as electromigration, diffusion, and voids arising from high fabrication temperatures can weaken interconnects and solder joints. Selecting materials that effectively conduct heat and closely match in expansion rates is critical, although choices are often restricted by process compatibility and cost considerations. Additionally, integrating microfluidic cooling and heat sinks presents further complexities.

Using fabrication processes compatible with the materials is important, as excessive heat can damage components. Thermocycling and accelerated aging tests can be used to evaluate long-term reliability. Voltage scaling and power gating should be used to minimize heat generation. To maintain uniform temperatures across layers, heat must spread efficiently. Thermal restrictions can be addressed with advanced packaging designs, material choices, and thermal interface materials.

#### 3.1 Thin film deposition and uniformity

The Through-Silicon Via (TSV) is integral to vertical interconnections in microelectronic devices but introduces a few challenges. Costs and cycle times increase when fabrication steps like etching, deposition, and planarization are added. TSVs must be precisely aligned to prevent electrical shorts, open circuits, or reduced performance. Having high aspect ratios makes etch depth control and sidewall uniformity difficult. In DRIE, the substrate can be damaged, affecting reliability. The TSVs can also cause thermal management issues and electromigration, resulting in voids and reduced reliability. The performance of devices can be affected by mechanical stresses during TSV fabrication. A thin wafer exposes TSVs, posing challenges in mechanical stability. Electrical leakage and crosstalk can occur when structures are densely packed, making proper dielectric isolation essential. It is crucial to test and comprehensively. Conducting non-TSVs destructive testing to detect defects, such as voids or cracks, is crucial. Fabrication of TSVs increases manufacturing costs due

Nanoscale Advances Review

to process complexity and the need for additional materials. The commercialization of 3D-integrated devices poses a significant challenge. Optimizing TSV fabrication, improving material properties, enhancing alignment techniques, and developing reliable testing methods require ongoing research. 3D microelectronics requires collaboration between semiconductor manufacturers, equipment providers, and research institutions.

#### 3.2 Testing and reliability

Testing and reliability considerations are crucial for fabricating 3D microelectronic devices, ensuring that they meet performance specifications and maintain functionality throughout their operational lifetime. Access constraints and interconnect testing present challenges in evaluating the functionality and reliability of 3D microelectronic devices. Yield monitoring, nondestructive testing, and long-term stability testing are essential for ensuring the reliability of 3D microelectronic devices. Collaboration between device designers, process engineers, reliability engineers, and testing specialists is essential for implementing effective testing and reliability strategies and ensuring the quality and performance of 3D microelectronic devices.

#### 3.3 Cost considerations

Material, equipment, and labor costs significantly impact fabrication expenses. Balancing testing requirements, R&D expenses, and packaging and assembly costs is crucial for costeffective manufacturing. Cost constraints heavily influence the fabrication of 3D microelectronic devices, manufacturing processes, material selection, equipment utilization, and overall production efficiency. Additionally, material waste and environmental compliance contribute to production costs. Strategies like recycling and sustainable practices help mitigate expenses. High-volume production lowers per-unit costs; however, initial setup costs and production ramp-up expenses should also be considered.

## 3.4 Integration of heterogeneous components

Integrating heterogeneous components in the fabrication of 3D microelectronic devices introduces several constraints and challenges stemming from differences in materials, processes, interfaces, and functionalities. Key considerations include material compatibility, process compatibility, dimensional mismatch, interfacial adhesion and bonding, thermal management, electrical interconnects, signal compatibility and interface design, reliability and durability, as well as testing and characterization. Addressing these constraints requires interdisciplinary collaboration among materials scientists, process engineers, device designers, and reliability experts to develop innovative integration techniques, materials compatibility guidelines, and testing methodologies tailored to the unique challenges of heterogeneous component integration in 3D microelectronic devices. Challenges include material and process compatibility. Issues like dimensional mismatches and thermal management must be addressed.

## 3.5 Environmental and sustainability constraints

The fabrication of 3D microelectronic devices presents several environmental and sustainability constraints that must be addressed to minimize environmental impact and promote sustainable manufacturing practices. Some key constraints in this regard are resource consumption, chemical usage and waste generation, emissions and air quality, water usage and contamination, energy consumption, and carbon footprint, waste generation and disposal, supply chain sustainability, product lifecycle management, regulatory compliance, corporate social responsibility. Addressing these environmental and sustainability constraints requires a holistic approach to manufacturing that integrates environmental considerations into all aspects of the production process, from materials sourcing and process design to waste management and product lifecycle management. Collaborative efforts among industry stakeholders, government agencies, academia, and environmental advocacy groups are essential for driving innovation and promoting sustainable practices in fabricating 3D microelectronic devices.

#### 3.6 Process control and monitoring

Process control and monitoring are essential aspects of fabricating 3D microelectronic devices, ensuring consistent performance, quality, and reliability throughout manufacturing. However, several constraints and challenges like complexity of process flows, dimensional variability, material compatibility, alignment and registration accuracy, process variability and yield losses, equipment and tooling constraints, real-time monitoring challenges, data management and analysis, environmental and safety considerations are associated with process control and monitoring in this context. Addressing these constraints requires continuous improvement efforts, investment in advanced process control technologies, employee training, and collaboration among interdisciplinary engineers, scientists, and technicians. By overcoming these challenges, semiconductor manufacturers can enhance process control and monitoring capabilities, improve product quality and yield, and drive innovation in 3D. Challenges include complex process flows and dimensional variability. It is essential to monitor material compatibility, alignment accuracy, and process variability.

### 3.7 Scaling and miniaturization

Scaling and miniaturization in the fabrication of 3D microelectronic devices introduce several constraints and challenges, primarily due to the shrinking dimensions of device features and the increasing complexity of fabrication processes. Here are some key constraints: lithography limitations, aspect ratio limitations, material constraints, interconnect scaling, thermal constraints, manufacturability constraints, metrology and inspection challenges, cost constraints, reliability concerns, and design complexity are associated with scaling and miniaturization. Addressing these constraints requires interdisciplinary collaboration among device designers, process Review Nanoscale Advances

engineers, materials scientists, and equipment manufacturers to develop innovative solutions, optimize fabrication processes, and overcome technical challenges associated with scaling and miniaturization in 3D microelectronic device fabrication.

#### Standardization 3.8

Standardizing the fabrication of 3D microelectronic devices faces numerous constraints and challenges due to the technology's intricate and fast-evolving nature. Key issues include heterogeneous integration, customization, rapid technological advancements, interdisciplinary collaboration, global supply chain complexities, intellectual property protection, cost management, regulatory compliance, and the integration of legacy systems and technologies, all of which contribute to market fragmentation. Despite these challenges, standardization offers substantial benefits such as interoperability, compatibility, cost efficiencies, and accelerated innovation. Addressing these hurdles demands proactive stakeholder engagement, effective communication, consensus-building, and a dedicated effort towards collaborative problem-solving and ongoing enhancement.

#### 3.9 Complexity in existing design tools

Design tools facilitate performance optimization, complexity management, and manufacturability. EDA software can be used for layout, simulation, and verification, as well as 3D integration and heterogeneous system design tools. FEA, FDM, and CFD may be used for thermal and mechanical analyses, along with electromagnetic simulation tools for signal integrity and electromagnetic interference (EMI). Through electrical and thermal co-design approaches, floorplans, partitions, and interconnects can all be optimized. Technology compatibility, accuracy, and scalability are possible issues. Multiphysics simulation capabilities may be integrated into design automation using machine learning and artificial intelligence.

# Conclusion and future scope

This paper highlights the significant challenges in developing 3D microelectronic devices and the available opportunities. It emphasizes the enormous improvements in performance and integration density that these technologies promise while stressing the necessity for innovative solutions to overcome heat dissipation, material compatibility, and fabrication complexity to achieve these advancements. As a result of 3D integration, the paper emphasizes the importance of pushing the boundaries of microelectronic device performance. It advocates for a multidisciplinary approach that combines academia, industry, and research institutions to tackle the existing hurdles and advance the field.

Several promising directions are being pursued for the future of 3D microelectronic devices, such as the following. There is a growing need for research on new materials and advanced fabrication techniques to improve device performance and reliability. As densely packed 3D structures continue to become more complex, it will be crucial to address thermal management challenges with innovative solutions to ensure their sustainability. Aside from this, the exploration of new interconnect technologies and the improvement of design methodologies will allow for higher data rates and optimized performances to be achieved. We want to highlight that there is a wide range of potential applications of 3D microelectronics in emerging areas such as IoT, artificial intelligence, and quantum computing, and efforts should focus on making these technologies more sustainable and cost-effective to ensure their widespread adoption and impact across several industries.

# Conflicts of interest

There are no conflicts to declare.

## References

- 1 A. Rafique, I. Ferreira, G. Abbas and A. C. Baptista, Nano-Micro Lett., 2023, 15(1), 1-58.

- 2 A. K. Worku and D. W. Ayele, Results Chem., 2023, 5, 100971.

- 3 J. Qin, H. Zhang, Z. Yang, X. Wang, P. Das, F. Zhou and Z.-S. Wu, J. Energy Chem., 2023, 81, 410-431.

- 4 H. Stapf, F. Selbmann, Y. Joseph and P. Rahimi, ACS Appl. Electron. Mater., 2024, 6, 2120-2133.

- Kalaiarasi, T. Deepa, S. Angalaeswari, D. Subbulekshmi and R. Kathiravan, J. Nanomater., 2021, 2021, 6244874.

- 6 T. A. Truong, T. K. Nguyen, H. Zhao, N. K. Nguyen, T. Dinh, Y. Park, T. Nguyen, Y. Yamauchi, N. T. Nguyen and H. P. Phan, Small, 2022, 18, 2105748.

- 7 Z. Torkashvand, F. Shayeganfar and A. Ramazani, Micromachines, 2024, 15, 175.

- 8 M. Shak Sadi and E. Kumpikaitė, Nanomaterials, 2022, 12, 2039.

- 9 F. Mokhtari, Z. Cheng, R. Raad, J. Xi and J. Foroughi, J. Mater. Chem. A, 2020, 8, 9496-9522.

- 10 R. Yuvaraj, A. Karuppannan, A. K. Panigrahy and R. Swain, Silicon, 2023, 15, 1739-1746.

- 11 E. S. Kumar, S. Kumar P., N. A. Vignesh and S. Kanithan, Silicon, 2022, 14, 8439-8447.

- 12 A. S. Geege and T. S. A. Samuel, Silicon, 2022, 1-14.

- 13 C. Li, J. Du, Y. Gao, F. Bu, Y. H. Tan, Y. Wang, G. Fu, C. Guan, X. Xu and W. Huang, Adv. Funct. Mater., 2022, 32, 2205317.

- 14 R. Gupta, A. Kumar, A. Biswas, R. Singh, A. Gehlot, S. V. Akram and A. S. Verma, J. Energy Storage, 2022, 55, 105591.

- 15 D. S. Kim, J. Bin Kim, D. W. Ahn, J. H. Choe, J. S. Kim, E. S. Jung and S. G. Pyo, Electron. Mater. Lett., 2023, 1-18.

- 16 J. M. Majikes and J. A. Liddle, Nanoscale, 2022, 14, 15586-15595.

- 17 C. Gu, A. B. Jia, Y. M. Zhang and S. X. A. Zhang, Chem. Rev., 2022, 122, 14679-14721.

- 18 R. Gupta, R. Singh, A. Gehlot, S. V. Akram, N. Yadav, R. Brajpuriya, A. Yadav, Y. Wu, H. Zheng, A. Biswas, E. Suhir, V. S. Yadav, T. Kumar and A. S. Verma, Nanoscale, 2023, 15, 4682-4693.

19 D. Karnaushenko, T. Kang, V. K. Bandari, F. Zhu and O. G. Schmidt, *Adv. Mater.*, 2020, 32, 1902994.

20 I. Taj and U. Farooq, Electronics, 2023, 12, 935.

Nanoscale Advances

- 21 M.-C. Chen, H.-Y. Chen, C.-Y. Lin, C.-H. Chien, T.-F. Hsieh, J.-T. Horng, J.-T. Qiu, C.-C. Huang, C.-H. Ho and F.-L. Yang, *Sensors*, 2012, **12**, 3952–3963.

- 22 L. Zhu, C. Jo and S. K. Lim, *IEEE Trans. Compon. Packag. Manuf. Technol.*, 2022, 12, 1969–1982.

- 23 X. Ma, Y. Wang, Y. Wang, X. Cai and Y. Han, CCF Trans. High Perform. Comput., 2022, 4, 43-52.

- 24 X. Guo, Z. Xue and Y. Zhang, *NPG Asia Mater.*, 2019, **11**(1), 1–7.

- 25 F. Wang, T. Zhang, R. Xie, A. Liu, F. Dai, Y. Chen, T. Xu, H. Wang, Z. Wang, L. Liao, J. Wang, P. Zhou and W. Hu, *Adv. Mater.*, 2023, 2301197.

- 26 T. Lu, S. Ji, W. Jin, Q. Yang, Q. Luo and T.-L. Ren, *Sensors*, 2023, 23, 2991.

- 27 H. Wang, W. Zhang, D. Ladika, H. Yu, D. Gailevičius, H. Wang, C. Pan, P. N. S. Nair, Y. Ke, T. Mori, J. Y. E. Chan, Q. Ruan, M. Farsari, M. Malinauskas, S. Juodkazis, M. Gu and J. K. W. Yang, Adv. Funct. Mater., 2023, 2214211.

- 28 Y. Wang, A. Ahmed, A. Azam, D. Bing, Z. Shan, Z. Zhang, M. K. Tariq, J. Sultana, R. T. Mushtaq, A. Mehboob, C. Xiaohu and M. Rehman, J. Manuf. Syst., 2021, 60, 709– 733.

- 29 J. M. Pearce and N. Sommerfeldt, Energies, 2021, 14, 834.

- 30 D. Karnaushenko, T. Kang, V. K. Bandari, F. Zhu and O. G. Schmidt, *Adv. Mater.*, 2020, 32, 1902994.

- 31 M. M. Nahar, B. Ma, K. Guye, Q. H. Chau, J. Padilla, M. Iyengar and D. Agonafer, *Appl. Therm. Eng.*, 2021, **194**, 117109.

- 32 J. M. Allwood, T. H. C. Childs, A. T. Clare, A. K. M. De Silva, V. Dhokia, I. M. Hutchings, R. K. Leach, D. R. Leal-Ayala, S. Lowth, C. E. Majewski, A. Marzano, J. Mehnen, A. Nassehi, E. Ozturk, M. H. Raffles, R. Roy, I. Shyha and S. Turner, J. Mater. Process. Technol., 2016, 229, 729–757.

- 33 J. Chen, Q. Peng, X. Peng, H. Zhang and H. Zeng, *Chem. Rev.*, 2022, **122**, 14594–14678.

- 34 X. Fan and A. Walther, Chem. Soc. Rev., 2022, 51, 4023-4074.

- 35 C. Tong, Springer Series in Materials Science, 2022, vol. 317, pp. 1–51.

- 36 A. Pajonk, A. Prieto, U. Blum and U. Knaack, *J. Build. Eng.*, 2022, **45**, 103603.

- 37 C. Lu, M. Hsieh, Z. Huang, C. Zhang, Y. Lin, Q. Shen, F. Chen and L. Zhang, *Engineering*, 2022, 17, 44–63.

- 38 A. Alfieri, S. B. Anantharaman, H. Zhang and D. Jariwala, *Adv. Mater.*, 2023, **35**, 2109621.

- 39 P. Kumar, R. Kumar, S. Kumar, M. K. Khanna, R. Kumar, V. Kumar and A. Gupta, *Magnetochemistry*, 2023, **9**, 73.

- 40 S. S. Parihar, S. Thomann, G. Pahwa, Y. S. Chauhan and H. Amrouch, *IEEE Open J. Circ. Syst.*, 2023, 4, 258–270.

- 41 J. T. Borenstein, G. Cummins, A. Dutta, E. Hamad, M. P. Hughes, X. Jiang, H. H. Lee, K. F. Lei, X. S. Tang, Y. Zheng and J. Chen, *Lab Chip*, 2023, 23, 4928–4949.

- 42 D. V. Christensen, R. Dittmann, B. Linares-Barranco, A. Sebastian, M. Le Gallo, A. Redaelli, S. Slesazeck,

- T. Mikolajick, S. Spiga, S. Menzel, I. Valov, G. Milano, C. Ricciardi, S. J. Liang, F. Miao, M. Lanza, T. J. Quill, S. T. Keene, A. Salleo, J. Grollier, D. Marković, A. Mizrahi, P. Yao, J. J. Yang, G. Indiveri, J. P. Strachan, S. Datta, E. Vianello, A. Valentian, J. Feldmann, X. Li, W. H. P. Pernice, H. Bhaskaran, S. Furber, E. Neftci, F. Scherr, W. Maass, S. Ramaswamy, J. Tapson, P. Panda, Y. Kim, G. Tanaka, S. Thorpe, C. Bartolozzi, T. A. Cleland, C. Posch, S. C. Liu, G. Panuccio, M. Mahmud, A. N. Mazumder, M. Hosseini, T. Mohsenin, E. Donati, S. Tolu, R. Galeazzi, M. E. Christensen, S. Holm, D. Ielmini and N. Pryds, *Neuromorph. Comput. Eng.*, 2022, 2, 022501.

- 43 R. Ur Rasool, H. F. Ahmad, W. Rafique, A. Qayyum, J. Qadir and Z. Anwar, *Future Internet*, 2023, **15**, 94.

- 44 S. Nižetić, P. Šolić, D. López-de-Ipiña González-de-Artaza and L. Patrono, *J. Clean. Prod.*, 2020, 274, 122877.

- 45 A. Ghasempour, Inventions, 2019, 4, 22.

- 46 S. Kumar, P. Tiwari and M. Zymbler, *J. Big Data*, 2019, **6**, 1–21.

- 47 C. D. Schuman, S. R. Kulkarni, M. Parsa, J. P. Mitchell, P. Date and B. Kay, *Nat. Comput. Sci.*, 2022, **2**, 10–19.

- 48 K. Berggren, Q. Xia, K. K. Likharev, D. B. Strukov, H. Jiang, T. Mikolajick, D. Querlioz, M. Salinga, J. R. Erickson, S. Pi, F. Xiong, P. Lin, C. Li, Y. Chen, S. Xiong, B. D. Hoskins, M. W. Daniels, A. Madhavan, J. A. Liddle, J. J. McClelland, Y. Yang, J. Rupp, S. S. Nonnenmann, K.-T. Cheng, N. Gong, M. A. Lastras-Montaño, A. A. Talin, A. Salleo, B. J. Shastri, T. F. de Lima, P. Prucnal, A. N. Tait, Y. Shen, H. Meng, C. Roques-Carmes, Z. Cheng, H. Bhaskaran, D. Jariwala, H. Wang, J. M. Shainline, K. Segall, J. J. Yang, K. Roy, S. Datta and A. Raychowdhury, Nanotechnology, 2021, 32, 012002.

- 49 Y. Chen, Y. Xie, L. Song, F. Chen and T. Tang, *Engineering*, 2020, **6**, 264–274.

- 50 M. A. Rosen and H. A. Kishawy, *Sustainability*, 2012, **4**, 154–174.

- 51 H. Hegab, N. Khanna, N. Monib and A. Salem, *Sustainable Mater. Technol.*, 2023, 35, e00576.

- 52 S. Saxena, M. Johnson, F. Dixit, K. Zimmermann, S. Chaudhuri, F. Kaka and B. Kandasubramanian, *Renew. Sustain. Energy Rev.*, 2023, 178, 113238.

- 53 A. Adel, J. Smart Cities, 2023, 6, 2742–2782.

- 54 H. Allioui and Y. Mourdi, Sensors, 2023, 23, 8015.

- 55 D. Karnaushenko, T. Kang, V. K. Bandari, F. Zhu and O. G. Schmidt, *Adv. Mater.*, 2020, 32, 1902994.

- 56 C. H. Rao, K. Avinash, B. K. S. V. L. Varaprasad and S. Goel, J. Electron. Mater., 2022, 51, 2747–2765.

- 57 Q. Hua and G. Shen, Chem. Soc. Rev., 2024, 53, 1316-1353.

- 58 D. Jayachandran, N. U. Sakib and S. Das, *Nat. Rev. Electr. Eng.*, 2024, **1**(5), 300–316.

- 59 T. D. Ngo, A. Kashani, G. Imbalzano, K. T. Q. Nguyen and D. Hui, *Compos. B Eng.*, 2018, **143**, 172–196.

- 60 Y. Qin, A. Brockett, Y. Ma, A. Razali, J. Zhao, C. Harrison, W. Pan, X. Dai and D. Loziak, *Int. J. Adv. Des. Manuf. Technol.*, 2010, 47, 821–837.

61 L. Wang, Z. Yi, Y. Zhao, Y. Liu and S. Wang, *Chem. Soc. Rev.*, 2023, 52, 795–835.

- 62 H. Chen, L. Guo, W. Zhu and C. Li, Polymers, 2022, 14, 4635.

- 63 G. L. Samuel, L. Kong, Y. Arcot and P. Pandit, *Materials Horizons: from Nature to Nanomaterials*, 2022, pp. 361–402.

- 64 C.-Y. Kang and Y.-S. Su, Micromachines, 2022, 13, 1534.

- 65 S. Lee, J. Kim, H. Kwon, D. Son, I. S. Kim and J. Kang, *Nano Energy*, 2023, **110**, 108379.

- 66 H. Liu, D. Liu, J. Yang, H. Gao and Y. Wu, Small, 2023, 19, 2206938.

- 67 Z. Cao, Y. Bian, T. Hu, Y. Yang, Z. Cui, T. Wang, S. Yang, X. Weng, R. Liang and C. Tan, *J. Materiomics*, 2023, 9, 930–958.

- 68 S. Liu, Z. Hou, L. Lin, Z. Li and H. Sun, *Adv. Funct. Mater.*, 2023, 2211280.

- 69 L. S. De Vasconcelos, R. Xu, Z. Xu, J. Zhang, N. Sharma, S. R. Shah, J. Han, X. He, X. Wu, H. Sun, S. Hu, M. Perrin, X. Wang, Y. Liu, F. Lin, Y. Cui and K. Zhao, *Chem. Rev.*, 2022, 122, 13043–13107.

- 70 R. Zhang, J. Jiang and W. Wu, Small Struct., 2022, 3, 2100120.

- 71 Z. Dong, Q. He, D. Shen, Z. Gong, D. Zhang, W. Zhang, T. Ono and Y. Jiang, *Microsyst. Nanoeng.*, 2023, 9, 31.

- 72 S. Scott and Z. Ali, Micromachines, 2021, 12, 319.

- 73 W. Pang, X. Cheng, H. Zhao, X. Guo, Z. Ji, G. Li, Y. Liang, Z. Xue, H. Song, F. Zhang, Z. Xu, L. Sang, W. Huang, T. Li and Y. Zhang, Natl. Sci. Rev., 2020, 7, 342–354.

- 74 H. Wang, J. Ma, Y. Yang, M. Gong and Q. Wang, Micromachines, 2023, 14, 1149.

- 75 M. C. McCorry, K. F. Reardon, M. Black, C. Williams, G. Babakhanova, J. M. Halpern, S. Sarkar, N. S. Swami, K. A. Mirica, S. Boermeester and A. Underhill, *Biofabrication*, 2022, 15, 012001.

- 76 J. E. Payne, P. Nyholm, R. Beazer, J. Eddy, H. Stevenson, B. Ferguson, S. Schultz and G. N. Nielson, *Sci. Rep.*, 2024, 14(1), 1–10.

- 77 K. Takahashi, Y. Taguchi, M. Tomisaka, H. Yonemura, M. Hoshino, M. Ueno, Y. Egawa, Y. Nemoto, Y. Yamaji, H. Terao, M. Umemoto, K. Kameyama, A. Suzuki, Y. Okayama, T. Yonezawa and K. Kondo, *Proc. Electron. Compon. Technol. Conf.*, 2004, 1, 601–609.

- 78 S. Zhang, Z. Li, H. Zhou, R. Li, S. Wang, K. W. Paik and P. He, *e-Prime Adv. Electr. Eng. Electron. Energy*, 2022, 2, 100052.

- 79 X. Guo, Z. Xue and Y. Zhang, NPG Asia Mater., 2019, 11, 29.

- 80 L. Zhou, X. Zhang and H. Xie, Micromachines, 2019, 10, 323.

- 81 R. Elkarous, A. Bardaoui, J. Borme, N. Sghaier, P. Alpuim, D. M. F. Santos and R. Chtourou, *Chemosensors*, 2023, 11, 181.

- 82 C. W. Lin, S. H. Chang, C. C. Huang and C. H. Lin, *Microelectron. Eng.*, 2020, 227, 111309.

- 83 A. C. Fischer, F. Forsberg, M. Lapisa, S. J. Bleiker, G. Stemme, N. Roxhed and F. Niklaus, *Microsyst. Nanoeng.*, 2015, **1**, 1–16.

- 84 C. T. Ko and K. N. Chen, *Microelectron. Reliab.*, 2013, 53, 7–16.

- 85 X. Guo, Z. Xue and Y. Zhang, NPG Asia Mater., 2019, 11, 29.

- 86 C. L. Chen, D. R. Yost, J. M. Knecht, J. Wey, D. C. Chapman,

D. C. Oakley, A. M. Soares, L. J. Mahoney, J. P. Donnelly,

C. K. Chen, V. Suntharalingam, R. Berger, W. Hu,

B. D. Wheeler, C. L. Keast and D. C. Shaver, *Microelectron. Eng.*, 2011, 88, 131–134.

- 87 X. Guo, Z. Xue and Y. Zhang, NPG Asia Mater., 2019, 11, 1-7.

- 88 M. A. Butt, C. Tyszkiewicz, M. Karasiński Pawełand Zięba, A. Kaźmierczak, M. Zdończyk, Ł. Duda, M. Guzik, J. Olszewski, T. Martynkien, A. Bachmatiuk and R. Piramidowicz, *Materials*, 2022, 15, 4591.

- 89 P. Lan, R. Gheisari, J. L. Meyer and A. A. Polycarpou, *Int. J. Precis. Eng. Manuf.*, 2020, 21, 1025–1034.

- 90 S. S. Ba Hashwan, M. H. M. Khir, I. M. Nawi, M. R. Ahmad, M. Hanif, F. Zahoor, Y. Al-Douri, A. S. Algamili, U. I. Bature, S. S. Alabsi, M. O. B. Sabbea and M. Junaid, *Discover Nano*, 2023, 18, 25.

- 91 H. Hamed, M. Eldiasty, S.-M. Seyedi-Sahebari and J. D. Abou-Ziki, *Mater. Today*, 2023, **66**, 194–220.

- 92 Y. Pandey and S. P. Singh, J. Inst. Eng. (India): B, 2023, 1-12.

- 93 H. Hamed, M. Eldiasty, S.-M. Seyedi-Sahebari and J. D. Abou-Ziki, *Mater. Today*, 2023, **66**, 194–220.

- 94 H. Kurt, P. Pishva, Z. S. Pehlivan, E. G. Arsoy, Q. Saleem and M. K. Bayazıt, *Anal. Chim. Acta*, 2021, **1185**, 338842.

- 95 K. R. Sinju, B. K. Bhangare, S. J. Patil, N. S. Ramgir, A. K. Debnath and D. K. Aswal, in *Nanotechnology-Based E-Noses*, Elsevier, 2023, pp. 101–124.

- 96 X. Guo, Z. Xue and Y. Zhang, NPG Asia Mater., 2019, 11, 29.

- 97 M. Huff, Micromachines, 2021, 12, 991.

- 98 S. Jambhulkar, D. Ravichandran, Y. Zhu, V. Thippanna, A. Ramanathan, D. Patil, N. Fonseca, S. V. Thummalapalli, B. Sundaravadivelan, A. Sun, W. Xu, S. Yang, A. M. Kannan, Y. Golan, J. Lancaster, L. Chen, E. B. Joyee and K. Song, *Small*, 2023, 2306394.

- 99 Z. Wan, H. Liu, Y. Zheng, Y. Ma, K. Liu, X. Zhou, C. Liu, K. Liu and E. Wang, Adv. Funct. Mater., 2023, 2303519.

- 100 K. Ariga, Chem. Mater., 2023, 35, 5233-5254.

- 101 K. Singh, A. Thakur, A. Awasthi and A. Kumar, *J. Mater. Sci.: Mater. Electron.*, 2020, **31**, 13158–13166.

- 102 K. Singh, M. Kaur, I. Chauhan, A. Awasthi, M. Kumar, A. Thakur and A. Kumar, *Ceram. Int.*, 2020, 46, 26233– 26237.

- 103 K. Singh, M. Kaur, I. Chauhan, H. Singh, A. Awasthi, M. Kumar, A. Thakur and A. Kumar, *J. Mater. Sci.: Mater. Electron.*, 2021, 32, 5556–5566.

- 104 N. Singh, R. Agarwal, A. Awasthi, P. K. Gupta and S. K. Mittal, *Atmos. Environ.*, 2010, 44, 1292–1300.

- 105 A. Awasthi, B. Sen Wu, C. N. Liu, C. W. Chen, S. N. Uang and C. J. Tsai, MAPAN-J. Metrol. Soc. India, 2013, 28, 205–215.

- 106 J. Allison, Appl. Therm. Eng., 2017, 114, 1498-1506.

- 107 A. Biswas, S. Lotha, R. Gupta, D. K. Avasthi and S. N. Paul, *J. Appl. Phys.*, 2002, **91**, 4922–4927.

- 108 M. Haji Bashi, L. De Tommasi, A. Le Cam, L. S. Relaño, P. Lyons, J. Mundó, I. Pandelieva-Dimova, H. Schapp, K. Loth-Babut, C. Egger, M. Camps, B. Cassidy, G. Angelov and C. E. Stancioff, *Renew. Sustain. Energy Rev.*, 2023, 172, 113055.

Nanoscale Advances

- 109 M. Azimian, R. Habibifar, V. Amir, E. Shirazi, M. S. Javadi, A. E. Nezhad and S. Mohseni, IEEE Access, 2023, 11, 72050-72069.

- 110 A. Kumar, N. Gupta, A. Jain, R. Gupta, B. Choudhary, K. Kumar, A. K. Goyal and Y. Massoud, Memories -Materials, Devices, Circuits and Systems, 2023, 6, 100087.

- 111 R. Gupta, R. Singh, A. Gehlot, S. V. Akram, N. Yadav, R. Brajpuriya, A. Yadav, Y. Wu, H. Zheng, A. Biswas, E. Suhir, V. S. Yadav, T. Kumar and A. S. Verma, Nanoscale, 2023, 15, 4682-4693.

- 112 Z. Chai, A. Childress and A. A. Busnaina, ACS Nano, 2022, 16, 17641-17686.

- 113 M. Mastrangeli, S. Abbasi, C. Varel, C. Van Hoof, J.-P. Celis and K. F. Böhringer, J. Micromech. Microeng., 2009, 19,

- 114 E. Arzt, H. Quan, R. M. McMeeking and R. Hensel, Prog. Mater. Sci., 2021, 120, 100823.

- 115 V. Harish, M. M. Ansari, D. Tewari, A. B. Yadav, N. Sharma, S. Bawarig, M. L. García-Betancourt, A. Karatutlu, M. Bechelany and A. Barhoum, J. Taiwan Inst. Chem. Eng., 2023, 149, 105010.

- 116 J. Ni, A. Dai, Y. Yuan, L. Li and J. Lu, Matter, 2020, 2, 1366-1376.

- 117 Z. Wang, Y. Chen, Y. Zhou, J. Ouyang, S. Xu and L. Wei, Nanoscale Adv., 2022, 4, 4237-4257.

- 118 Y. Li, J. Qu, F. Li, Z. Qu, H. Tang, L. Liu, M. Zhu and O. G. Schmidt, Nano Mater. Sci., 2021, 3, 140-153.

- 119 J. Feng, D. Zheng, X. Gao, W. Que, W. Shi, W. Liu, F. Wu and X. Cao, Front. Energy Res., 2020, 8, 210.

- 120 S. Rajagopal, R. Pulapparambil Vallikkattil, M. Mohamed Ibrahim and D. G. Velev, Condens. Matter, 2022, 7, 6.

- 121 F. Li, A. Hu, X. Zhao, T. Wu, W. Chen, T. Lei, Y. Hu, M. Huang and X. Wang, J. Mater. Chem. A, 2022, 10, 14051-14059.

- 122 P. Zhang, F. Wang, M. Yu, X. Zhuang and X. Feng, Chem. Soc. Rev., 2018, 47, 7426-7451.

- 123 W. Liu, Nanostructured Materials for Next-Generation Energy Storage and Conversion, 2019, pp. 205-262.

- 124 D. Karnaushenko, T. Kang, V. K. Bandari, F. Zhu and O. G. Schmidt, Adv. Mater., 2020, 32, 1902994.

- 125 H. Hassanin, G. Sheikholeslami, P. Sareh and R. B. Ishaq, Adv. Eng. Mater., 2021, 23, 2100422.

- 126 X. Guo, Z. Xue and Y. Zhang, NPG Asia Mater., 2019, 11, 29.

- 127 G. Liu, X. Zhang, X. Chen, Y. He, L. Cheng, M. Huo, J. Yin, F. Hao, S. Chen, P. Wang, S. Yi, L. Wan, Z. Mao, Z. Chen, X. Wang, Z. Cao and J. Lu, Mater. Sci. Eng. R Rep., 2021, 145, 100596.

- 128 S. C. Ligon, R. Liska, J. Stampfl, M. Gurr and R. Mülhaupt, Chem. Rev., 2017, 117, 10212-10290.

- 129 C. Park, B. Lee, J. Kim, H. Lee, J. Kang, J. Yoon, J. Ban, C. Song and S. J. Cho, *Polymers*, 2022, 14, 1232.

- 130 T. van Manen, S. Janbaz and A. A. Zadpoor, Mater. Horiz., 2017, 4, 1064-1069.

- 131 Z. Chen, Z. Li, J. Li, C. Liu, C. Lao, Y. Fu, C. Liu, Y. Li, P. Wang and Y. He, J. Eur. Ceram. Soc., 2019, 39, 661-687.

132 J. Deng, H. Ji, C. Yan, J. Zhang, W. Si, S. Baunack, S. Oswald, Y. Mei and O. G. Schmidt, Angew. Chem., Int. Ed., 2013, 52, 2326-2330.

- 133 J. Reeder, M. Kaltenbrunner, T. Ware, D. Arreaga-Salas, A. Avendano-Bolivar, T. Yokota, Y. Inoue, M. Sekino, W. Voit, T. Sekitani and T. Someya, Adv. Mater., 2014, 26, 4967-4973.

- 134 J. H. Cho, M. D. Keung, N. Verellen, L. Lagae, V. V. Moshchalkov, P. Van Dorpe and D. H. Gracias, Small, 2011, 7, 1943-1948.

- 135 W. Lee, Y. Liu, Y. Lee, B. K. Sharma, S. M. Shinde, S. D. Kim, K. Nan, Z. Yan, M. Han, Y. Huang, Y. Zhang, J. H. Ahn and J. A. Rogers, Nat. Commun., 2018, 9, 1-9.

- 136 J. Sun, J. Hensel, M. Köhler and K. Dilger, J. Manuf. Process., 2021, 65, 97-111.

- 137 A. Mostafaei, A. M. Elliott, J. E. Barnes, F. Li, W. Tan, C. L. Cramer, P. Nandwana and M. Chmielus, Prog. Mater. Sci., 2021, 119, 100707.

- 138 S. Siddiqui, S. Surananai, K. Sainath, M. Zubair Khan, R. Raja Pandiyan Kuppusamy and Y. Kempaiah Suneetha, Eur. Polym. J., 2023, 196, 112298.

- 139 J. Ahn, J.-H. Ha, Y. Jeong, Y. Jung, J. Choi, J. Gu, S. H. Hwang, M. Kang, J. Ko, S. Cho, H. Han, K. Kang, J. Park, S. Jeon, J.-H. Jeong and I. Park, Nat. Commun., 2023, 14, 833.

- 140 X. Guo, Z. Xue and Y. Zhang, NPG Asia Mater., 2019, 11, 29.

- 141 P. Zhang, F. Wang, M. Yu, X. Zhuang and X. Feng, Chem. Soc. Rev., 2018, 47, 7426-7451.

- 142 A. Dalal, M. Mishra, S. Chakrabarti, R. K. Gupta and A. Mondal, Vacuum, 2022, 201, 111115.

- 143 C. Sheng, X. Dong, Y. Zhu, X. Wang, X. Chen, Y. Xia, Z. Xu, P. Zhou, J. Wan and W. Bao, Adv. Funct. Mater., 2023, 2304778.

- 144 D. Karnaushenko, T. Kang, V. K. Bandari, F. Zhu and O. G. Schmidt, Adv. Mater., 2020, 32, 1902994.

- 145 G. De Pasquale, Micromachines, 2021, 12, 1374.

- 146 S. Preetam, B. K. Nahak, S. Patra, D. C. Toncu, S. Park, M. Syväjärvi, G. Orive and A. Tiwari, Biosens. Bioelectron.: X, 2022, 10, 100106.

- 147 C. J. Taylor, A. Pomberger, K. C. Felton, R. Grainger, M. Barecka, T. W. Chamberlain, R. A. Bourne, C. N. Johnson and A. A. Lapkin, Chem. Rev., 2023, 123, 3089-3126.

- 148 C. Gu, A. B. Jia, Y. M. Zhang and S. X. A. Zhang, Chem. Rev., 2022, 122, 14679-14721.

- 149 S. B. Joseph, E. G. Dada, A. Abidemi, D. O. Oyewola and B. M. Khammas, Heliyon, 2022, 8, e09399.

- 150 C. Gu, A. B. Jia, Y. M. Zhang and S. X. A. Zhang, Chem. Rev., 2022, 122, 14679-14721.

- 151 A. Amiri, A. Bruno and A. A. Polycarpou, Carbon Energy, 2023, 5, e320.

- 152 P. Manickam, S. A. Mariappan, S. M. Murugesan, Hansda, Kaushik, Shinde A. S. P. Thipperudraswamy, Biosens. J., 2022, 12, 562.

- 153 A. Uddin, K. Milaninia, C.-H. Chen and L. Theogarajan, IEEE Trans. Compon. Packag. Manuf. Technol., 2011, 1, 1996-2004.

154 H. Wang, J. Ma, Y. Yang, M. Gong and Q. Wang, *Micromachines*, 2023, **14**, 1149.

- 155 P. Gadfort and P. D. Franzon, in 2009 IEEE 18th Conference on Electrical Performance of Electronic Packaging and Systems, IEEE, 2009, pp. 37–40.

- 156 A. Wali and S. Das, Adv. Funct. Mater., 2023, 2308129.

- 157 T. Ohba, K. Sakui, S. Sugatani, H. Ryoson and N. Chujo, *Electronics*, 2022, **11**, 236.

- 158 Z. Chen, J. Zhang, S. Wang and C.-P. Wong, *Fundam. Res.*, 2023, DOI: 10.1016/j.fmre.2023.04.014.

- 159 J. Wang, F. Duan, Z. Lv, S. Chen, X. Yang, H. Chen and J. Liu, *Appl. Sci.*, 2023, **13**, 8301.

- 160 C. M. Didier, A. Kundu, D. DeRoo and S. Rajaraman, J. Micromech. Microeng., 2020, 30, 103001.

- 161 S. Kumar and K. M. Gangawane, *Advanced Computational Approaches for Water Treatment*, 2023, pp. 61–77.

- 162 Z. S. Siwy, M. L. Bruening and S. Howorka, *Chem. Soc. Rev.*, 2023, 52, 1983–1994.

- 163 H. S. Khoo, C. Lin, S.-H. Huang and F.-G. Tseng, Micromachines, 2011, 2, 17–48.

- 164 D. Karnaushenko, T. Kang, V. K. Bandari, F. Zhu and O. G. Schmidt, Adv. Mater., 2020, 32, 1902994.

- 165 H. Li, H. Liu, M. Sun, Y. Huang and L. Xu, Adv. Mater., 2021, 33, 2004425.

- 166 D. Karnaushenko, T. Kang and O. G. Schmidt, Adv. Mater. Technol., 2019, 4, 1800692.

- 167 N. P. Dharmarajan, D. Vidyasagar, J.-H. Yang, S. N. Talapaneni, J. Lee, K. Ramadass, G. Singh, M. Fawaz, P. Kumar and A. Vinu, Adv. Mater., 2023, 2306895.

- 168 H. Liu, Y. Yao and P. Samorì, *Small Methods*, 2023, 7, 2300468.

- 169 A. Biswas, S. Lotha, R. Gupta, D. K. Avasthi and S. N. Paul, *J. Appl. Phys.*, 2002, **91**, 4922–4927.

- 170 A. Biswas, R. Gupta, N. Kumar, D. K. Avasthi, J. P. Singh, S. Lotha, D. Fink, S. N. Paul and S. K. Bose, *Appl. Phys. Lett.*, 2001, 78, 4136–4138.

- 171 A. Biswas, D. K. Avasthi, D. Fink, J. Kanzow, U. Schürmann, S. J. Ding, O. C. Aktas, U. Saeed, V. Zaporojtchenko, F. Faupel, R. Gupta and N. Kumar, *Nucl. Instrum. Methods Phys. Res., Sect. B*, 2004, 217, 39–50.

- 172 P. Cai, C. Wang, H. Gao and X. Chen, *Adv. Mater.*, 2021, 33, 2007977.

- 173 P. Zhang, S. Yang, H. Xie, Y. Li, F. Wang, M. Gao, K. Guo, R. Wang and X. Lu, *ACS Nano*, 2022, **16**, 17593–17612.

- 174 Y. Li, S. Xiao, T. Qiu, X. Lang, H. Tan, Y. Wang and Y. Li, *Energy Storage Mater.*, 2022, **45**, 741–767.

- 175 N. Nandihalli, C.-J. Liu and T. Mori, *Nano Energy*, 2020, 78, 105186.

- 176 N. Nandihalli, C.-J. Liu and T. Mori, *Nano Energy*, 2020, 78, 105186.

- 177 A. K. Aliyana and G. Stylios, Adv. Sci., 2023, 10, 2304232.

- 178 O. D. Abodunrin, K. El Mabrouk and M. Bricha, *J. Mater. Chem. B*, 2023, **11**, 955–973.

- 179 J. Zhang, Y. Wang, B. J. Rodriguez, R. Yang, B. Yu, D. Mei, J. Li, K. Tao and E. Gazit, *Chem. Soc. Rev.*, 2022, 51, 6936–6947.

- 180 J. C. Hsu, C. H. Hsu and Y. W. Huang, *Micromachines*, 2019, **10**, 52.

- 181 H. Fu, K. Nan, P. Froeter, W. Huang, Y. Liu, Y. Wang, J. Wang, Z. Yan, H. Luan, X. Guo, Y. Zhang, C. Jiang, L. Li, A. C. Dunn, X. Li, Y. Huang, Y. Zhang and J. A. Rogers, Small, 2017, 13, 1700151.

- 182 Z. Yan, M. Han, Y. Shi, A. Badea, Y. Yang, A. Kulkarni, E. Hanson, M. E. Kandel, X. Wen, F. Zhang, Y. Luo, Q. Lin, H. Zhang, X. Guo, Y. Huang, K. Nan, S. Jia, A. W. Oraham, M. B. Mevis, J. Lim, X. Guo, M. Gao, W. Ryu, K. J. Yu, B. G. Nicolau, A. Petronico, S. S. Rubakhin, J. Lou, P. M. Ajayan, K. Thornton, et al., Proc. Natl. Acad. Sci. U. S. A., 2017, 114, E9455.

- 183 S. Bernabé, T. Tekin, B. Sirbu, J. Charbonnier, P. Grosse and M. Seyfried, in *Integrated Nanophotonics*, Wiley, 2023, pp. 1–52.

- 184 T. Chaloun, S. Brandl, N. Ambrosius, K. Kröhnert, H. Maune and C. Waldschmidt, *IEEE J. Microw.*, 2023, 3, 783–799.

- 185 U. Matthew, J. Kazaure and N. Okafor, *EAI Endorsed Trans. Cloud Syst.*, 2018, 7, 169173.

- 186 T. E. Kazior, Philos. Trans. R. Soc., A, 2014, 372, 20130105.

- 187 Y. Li and D. Goyal, *Springer Series in Advanced Microelectronics*, 2021, vol. 64, pp. 1–16.

- 188 Y. Liu, Microelectron. Reliab., 2010, 50, 514-521.

- 189 B. Wu and A. Kumar, Appl. Phys. Rev., 2014, 1, 11104.

- 190 Y. Liu, Microelectron. Reliab., 2010, 50, 514-521.

- 191 S. Rouf, A. Raina, M. Irfan Ul Haq, N. Naveed, S. Jeganmohan and A. Farzana Kichloo, Adv. Ind. Eng. Polym. Res., 2022, 5, 143–158.

- 192 A. Jandyal, I. Chaturvedi, I. Wazir, A. Raina and M. I. Ul Haq, *Sustain. Oper. Comput.*, 2022, 3, 33–42.

- 193 M. M. Shulaker, G. Hills, R. S. Park, R. T. Howe, K. Saraswat, H.-S. P. Wong and S. Mitra, *Nature*, 2017, **547**, 74–78.

- 194 J. Y. Kim, X. Ju, K. W. Ang and D. Chi, *ACS Nano*, 2023, 17, 1831–1844.

- 195 A. Darwish and A. E. Hassanien, *Sensors*, 2011, **11**, 5561-5595.

- 196 A. Passian and N. Imam, Sensors, 2019, 19, 4048.

- 197 M. Azlin, R. Ilyas, M. Zuhri, S. Sapuan, M. Harussani, S. Sharma, A. Nordin, N. Nurazzi and A. Afiqah, *Polymers*, 2022, **14**, 180.

- 198 M. Tan, J. Xu, S. Liu, J. Feng, H. Zhang, C. Yao, S. Chen, H. Guo, G. Han, Z. Wen, B. Chen, Y. He, X. Zheng, D. Ming, Y. Tu, Q. Fu, N. Qi, D. Li, L. Geng, S. Wen, F. Yang, H. He, F. Liu, H. Xue, Y. Wang, C. Qiu, G. Mi, Y. Li, T. Chang, M. Lai, L. Zhang, Q. Hao and M. Qin, Front. Optoelectron., 2023, 16, 1.

- 199 D. Bhattacharya and N. K. Jha, *Adv. Electron.*, 2014, **2014**, 1–21.

- 200 S. Bhukya and B. R. Nistala, *Microelectron. J.*, 2023, 139, 105907.

- 201 P. Raut, U. Nanda and D. K. Panda, *ECS J. Solid State Sci. Technol.*, 2023, **12**, 031010.

- 202 A. Navaneetha and K. Bikshalu, Electronics, 2023, 12, 1407.

- 203 M. Pons, E. Valenzuela, B. Rodríguez, J. A. Nolazco-Flores and C. Del-Valle-Soto, *Sensors*, 2023, 23, 3876.

Nanoscale Advances

- 204 K. Pahlavan and P. Krishnamurthy, Int. J. Wirel. Inf. Netw., 2021, 28, 3-19,

- 205 A. Darwish and A. E. Hassanien, Sensors, 2011, 11, 5561-5595.

- 206 M.-F. Lai, S.-W. Li, J.-Y. Shih and K.-N. Chen, Microelectron. Eng., 2011, 88, 3282-3286.

- 207 P. Sethi and S. R. Sarangi, J. Electr. Comput. Eng., 2017,

- 208 J. Jeong, D.-M. Geum and S. Kim, Electronics, 2022, 11,

- 209 S. Phuyal, D. Bista and R. Bista, Sustain. Futures, 2020, 2, 100023.

- 210 M. Majid, S. Habib, A. R. Javed, M. Rizwan, G. Srivastava, T. R. Gadekallu and J. C.-W. Lin, Sensors, 2022, 22, 2087.

- 211 Y. Chen, Engineering, 2017, 3, 588-595.

- 212 P. Ekaterina, V. Peter, D. Smirnova, C. Vyacheslav and B. Ilya, Sci. Rep., 2023, 13, 10561.

- 213 J. Miya, S. Raj, M. A. Ansari, S. Kumar and R. Kumar, in 6G Enabled Fog Computing in IoT, Springer Nature Switzerland, Cham, 2023, pp. 355-394.

- 214 L. M. S. do Nascimento, L. V. Bonfati, M. L. B. Freitas, J. J. A. Mendes Junior, H. V. Siqueira and S. L. Stevan, Sensors, 2020, 20, 4063.

- 215 C. Lécuyer, Enterp. Soc., 2022, 23, 133-163.

- 216 J. Wu, Y.-L. Shen, K. Reinhardt, H. Szu and B. Dong, Appl. Comput. Intell. Soft Comput., 2013, 2013, 1-13.

- 217 N. Margalit, C. Xiang, S. M. Bowers, A. Bjorlin, R. Blum and J. E. Bowers, Appl. Phys. Lett., 2021, 118, 220501.

- 218 C. Lian, C. Vagionas, T. Alexoudi, N. Pleros, N. Youngblood and C. Ríos, Nanophotonics, 2022, 11, 3823-3854.

- 219 T. B. Taha, A. A. Barzinjy, F. H. S. Hussain and T. Nurtayeva, Memories - Materials, Devices, Circuits and Systems, 2022, 2, 100011.

- 220 H. Byun, J. Bok, K. Cho, K. Cho, H. Choi, J. Choi, S. Choi, S. Han, S. Hong, S. Hyun, T. J. Jeong, H.-C. Ji, I.-S. Joe, B. Kim, D. Kim, J. Kim, J.-K. Kim, K. Kim, S.-G. Kim, D. Kong, B. Kuh, H. Kwon, B. Lee, H. Lee, K. Lee, S. Lee, K. Na, J. Nam, A. Nejadmalayeri, Y. Park, S. Parmar, J. Pyo, D. Shin, J. Shin, Y. Shin, S.-D. Suh, H. Yoon, Y. Park, J. Choi, K.-H. Ha and G. Jeong, Photon. Res., 2014, 2, A25.

- 221 M. A. Butt, Encyclopedia, 2023, 3, 824-838.