# **RSC** Advances

View Article Online

View Journal | View Issue

# PAPER

Check for updates

Cite this: RSC Adv., 2024, 14, 6058

Received 11th December 2023 Accepted 18th January 2024

DOI: 10.1039/d3ra08447g

rsc.li/rsc-advances

# 1. Introduction

Thin film transistors (TFTs) have attracted much interest due to their ever-growing application in liquid-crystal matrix displays and radio frequency identification tags.<sup>1-3</sup> Typically, polycrystalline and amorphous silicon thin films have been used as the semiconducting layer thanks to their material abundance in nature and mature fabrication process. However, the low electron mobility and non-transparency in the visible range of (polycrystalline and amorphous) silicon thin films hinder further development, for instance, as portable electronics driven by battery-supplied voltages.<sup>4-6</sup> Thus, metal-oxide semiconductors, such as TiO<sub>2</sub>, ZnO, InGaZnO, and InZnO, have emerged as promising alternatives with their outstanding properties including larger energy bandgap, higher electron mobility, optical transparency, and better film uniformity.<sup>7-11</sup> In

# Low voltage-driven, high-performance TiO<sub>2</sub> thin film transistors with MHz switching speed<sup>+</sup>

Xiaoping Chen,<sup>abc</sup> Jiancong Ni,<sup>abc</sup> Weiqiang Yang, <sup>(D) abc</sup> Shaoying Ke<sup>\*d</sup> and Maosheng Zhang <sup>(D) \*abc</sup>

High-speed circuits based on thin film transistors (TFTs) show promising potential applications in biomedical imaging and human-machine interactions. One of the critical requirements for high-speed electronic devices lies in high-frequency switching or amplification at low voltages, typically driven by batteries (~3.0 V). To date, however, most electrical performances of metal oxide TFTs are measured under direct current (DC) conditions, and their dynamic switching behaviour is scarcely explored and studied systematically. Here in this work, we present low voltage-driven, high-performance TiO<sub>2</sub> thin film transistors, which can be operated at a switching speed of MHz. Our proposed TiO<sub>2</sub> TFTs demonstrated a high on-off ratio of  $10^7$ , together with a subthreshold swing (SS) of ~150 mV Dec<sup>-1</sup> averaged over four orders of magnitude, which can be further reduced below 100 mV Dec<sup>-1</sup> when the temperature cools to 77 K. Additionally, the TiO<sub>2</sub> TFTs exhibit excellent gate-pulse switching at various frequencies ranging from 1.0 Hz to 1.0 MHz. We also explored the potential application of the TiO<sub>2</sub> TFTs as logic gates by constructing a resistive-loaded inverter, which shows stable operation at 10 kHz frequency and various temperatures. Thus, our results show the great potential of TiO<sub>2</sub> TFTs as a new platform for high-speed electronic applications.

particular, titanium oxide (TiO<sub>2</sub>) has shown great potential as an active channel material in n-type TFTs owning to its superior advantages such as low cost, material abundance, non-toxicity, and mechanical stability. Although tremendous efforts have been devoted to improving the electrical performance of TiO<sub>2</sub> TFTs operated at battery-supply voltages, most electrical performances of TiO<sub>2</sub> TFTs have been focused on DC operation, and the corresponding dynamic switching behaviour is typically ignored and not reported as a figure of merit.<sup>12-14</sup> In recent years, high-speed circuits based on thin film transistors have shown promising potential applications in biomedical imaging and human–machine interactions.<sup>15-17</sup> In this regard, it is crucial to implement reliable, stable, and high-speed switching thin film transistors with a sufficiently high on/off ratio, an acceptable carrier mobility, and a low-driven voltage.

In this paper, we fully investigate the static DC performance and dynamic switching behaviour of the proposed TiO<sub>2</sub> thin film transistors including on-off ratios as high as  $10^7$ , subthreshold swings of averaged 150 mV Dec<sup>-1</sup> (four orders of magnitude), a contact resistance of 0.13  $\Omega$  cm<sup>2</sup>, an effective mobility of 3.87 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and a gate-pulse switching frequency beyond 1.0 MHz. Furthermore, the potential application of the TiO<sub>2</sub> TFTs as logic gates is explored *via* the construction of a resistive-loaded inverter, which can operate at 10 kHz frequency with a gain of 4.8 V V<sup>-1</sup>. Our work shows a tremendous potential of TiO<sub>2</sub> TFTs as fast-switching speed matrix displays and high-speed logic operations.

<sup>&</sup>lt;sup>a</sup>Department of Chemistry, School of Chemistry and Chemical Engineering and Environment, Minnan Normal University, Zhangzhou 36300, China. E-mail: zms0557@mnnu.edu.cn

<sup>&</sup>lt;sup>b</sup>Fujian Provincial Key Laboratory of Modern Analytical Science and Separation Technology, Minnan Normal University, Zhangzhou, 363000, China

Fujian Provincial University Key Laboratory of Pollution Monitoring and Control, Minnan Normal University, Zhangzhou 36300, China

<sup>&</sup>lt;sup>d</sup>College of Physics and Information Engineering, Minnan Normal University, Zhangzhou 363000, China. E-mail: syke@mnnu.edu.cn

<sup>†</sup> Electronic supplementary information (ESI) available. See DOI: https://doi.org/10.1039/d3ra08447g

### 2. Experimental

### 2.1 Device fabrication

Fig. S1<sup>†</sup> illustrates the stepwise fabrication process flow and the corresponding cross-section schematic for TiO<sub>2</sub> thin film transistors. The TiO<sub>2</sub> thin film transistors were fabricated using Si-SiO<sub>2</sub> substrates and the thickness of SiO<sub>2</sub> dielectric is 285 nm. Thermally activated atomic layer deposition (ALD) was then utilized to deposit TiO<sub>2</sub> as channel materials, which was then annealed at 500 °C for 30 min in an oxygen atmosphere for better thin film quality. The TiO<sub>2</sub> layer was deposited at a relatively low temperature (~250 °C) and its thickness was controlled by the cycling loops (0.12 nm for each cycle).  $TiO_2$ strips were then etched using the ICP dry etching system and CF<sub>4</sub>/Ar mixture was used as the etching gas. The etched region was defined by a standard photo-lithography procedure using a direct laser writer. AZ1500 photoresist was spin-coated and the baking temperature was 100 °C for 1 min. Another photolithography step was repeated to define the source and drain areas, and double layers of metal Al/Pt (50/30 nm) were then sputtered onto the substrate. Al was selected as the contact metal since a good ohmic contact can be formed between Al and TiO<sub>2</sub> annealed at 450 °C for 5 min, while Pt is used as a capping layer to prevent the Al layer from oxidization.<sup>18</sup> A layer of Al<sub>2</sub>O<sub>3</sub> dielectric with a thickness of 8 nm was chosen as the insulating gate oxide, which was deposited by plasma-enhanced ALD technique at a low temperature of 350 °C. Finally, the top gate region was defined by another photo-lithography step and double layers of Ti/Pt (10/50 nm) were then deposited as contact metals. To improve the quality of the TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> interface, the fabricated devices are annealed at 400 °C for 30 min (Ar/H<sub>2</sub>). The thickness of each layer is labeled accordingly in the corresponding cross-section illustrations.

#### 2.2 Material characterization

To investigate the TiO<sub>2</sub> film quality as the channel material, the X-ray diffraction technique, and the optical ellipsometry measurement were utilized to characterize the crystalline phase, film thickness, and uniformity. X-ray diffraction (XRD) was performed via Empyrean equipment, and the 2 theta linearity over the whole range is equal to or better than  $\pm 0.1^{\circ}$ . The optical ellipsometry measurement was conducted by an imaging Ellipsometer Nanofilm-ep4 (spectral range: 250-1700 nm). The highest lateral resolution of Nanofilm-ep4 is around 300 nm, which can be used to measure the thickness and the optical index over the smallest area of 1 µm<sup>2</sup>. Raman spectra were collected via LabRAM HR Evolution Confocal Raman Microscope. The wavelength of the scanning laser is located at 325 nm, and the Raman shift ranges from 100  $cm^{-1}$  to 800 cm<sup>-1</sup>. X-ray photoelectron spectroscopy (XPS) measurement of TiO<sub>2</sub> thin film before and after O<sub>2</sub> annealing was conducted using Thermo Fisher ESCALAB XI+ and the incident energy of Xray (Al Ka) is set to be 1486.6 eV, which allows high-resolution surface element analysis. The surface roughness of TiO<sub>2</sub> thin film was visualized using atomic force microscopy (AFM, Cypher S/Oxford Instruments Asylum Research) and the

corresponding profile images were collected at an area of  $1\times 1~\mu m^2$  under fast scan mode. All the material characterization was conducted at room temperature and atmosphere.

#### 2.3 Electrical measurement setup

The electrical measurement was performed within a six-arm low-temperature Lakeshore vacuumed probe station, which consists of four DC probes and two high-frequency tips. The available temperature range starts from 77 K to 350 K. The temperature-dependent electrical data was collected when the chamber heated up for higher temperature accuracy. DC probes were directly approached to metallic pads and the silicon substrate was connected to the stage using conductive tapes. The electrical signals were applied and visualized via an Agilent B1500A semiconductor device analyzer, which allows various modes of sweeping I(V), fast I(V) scan, and C(V) measurement. The applied maximum voltage can be up to 200 V with a maximum current of 1 A. The current resolution at room temperature is at the order of a few fA if grounded appropriately. In terms of the fast I(V) scan mode, a waveform-generating module was utilized to apply arbitrary and programmable electrical signals at a pulse width of 10 ns. Meanwhile, the minimum collection speed is limited to 10 ns and it should be noted that the signal noise increases significantly as the collection time shortens. In terms of the dynamic response of resistive-loaded inverters, the input signals were generated via a function generator (Keysight 33500B true form generator), which offers a maximum frequency (~100 MHz) of square waveforms. At the same time, the fast-switching electrical signals were collected and visualized by a digital bench oscilloscope (Tektronix TBS2074B series). To prevent the electrical propagation loss and crosstalk of high-speed signals, all the electrical connections were connected via broad-bandwidth SMU cables.

### 3. Results and discussion

# 3.1 Device schematics and transistor performance at T = 300 K

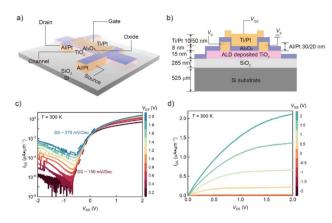

Fig. 1a shows the schematic illustration of TiO<sub>2</sub> thin film transistors fabricated on top of SiO<sub>2</sub>/Si substrates. Thermally activated atomic layer deposition (ALD) was utilized to deposit  $\sim$ 15 nm TiO<sub>2</sub> as channel materials followed by annealing at 500 °C for 30 min in an oxygen atmosphere to improve the crystalline and mobility. Another layer of Al<sub>2</sub>O<sub>3</sub> (~8 nm) was chosen as the insulating oxide due to its excellent film quality and large bandgap.<sup>18-20</sup> Fig. 1b illustrates the corresponding cross-section view, where Al was selected as the contact metal since a good ohmic contact can be formed between Al and TiO<sub>2</sub> without annealing, while Pt is used as a capping layer to prevent the Al layer from oxidization. In addition, double layers of Ti/Pt (10/50 nm) function as top gate contacts. An overview of device fabrication is well-elaborated in Fig. S1.† The active device area of TiO<sub>2</sub> TFTs is 18 (length)  $\times$  10 (width) mm<sup>2</sup>, while the contact pads are designed as 100  $\times$  100  $\text{mm}^2$  for probe electrical measurement (Fig. S2<sup>†</sup>). The film quality and thickness of the

**Fig. 1** Device schematics and transistor performance. (a) Schematic illustration of TiO<sub>2</sub> thin film transistors and the electrical connection. (b) Cross-section structure diagram with labeled thickness for each layer. (c) Room temperature transfer curves ( $I_{DS}-V_{GS}$ ) of TiO<sub>2</sub> TFTs collected at constant  $V_{DS}$  ranging from 0.2 V to 2.0 V at an interval of 0.2 V. (d) Output characteristics ( $I_{DS}-V_{DS}$ ) as a function of  $V_{GS}$  ranging from -2.0 V to +2.0 V in 0.5 V step.

annealed TiO<sub>2</sub> thin film as channel material were investigated via XRD, Raman, XPS, AFM, and optical ellipsometry techniques, respectively. Our result suggests that the as-deposited TiO<sub>2</sub> thin films show an amorphous phase and the formation of anatase polycrystalline phase after O2 annealing was confirmed based on XRD and Raman spectra (Fig. S3<sup>†</sup>).<sup>21,22</sup> Typically, the electron mobility of crystallized TiO<sub>2</sub> thin film is much better than the counterpart of amorphous phase due to less traps and lattice scattering.23-25 Meanwhile, the XPS result suggests that the annealing process may remove the defects of non-totally oxidized Ti, therefore improving the crystalline lattice and electron mobility (Fig. S4<sup>†</sup>).<sup>26,27</sup> Furthermore, the thickness and surface uniformity were characterized by optical ellipsometry and AFM technique, where the averaged thickness is 15.8  $\pm$  0.4 nm (Fig. S5<sup>†</sup>) and surface roughness is around 0.3 nm (Fig. S6<sup>†</sup>).

Fig. 1c presents the subthreshold characteristics of TiO<sub>2</sub> TFTs at various drain-to-source voltages  $(V_{DS})$ , where negligible hysteresis window was observed. Our proposed TiO<sub>2</sub> TFTs demonstrated a negative turn-on voltage, a significant on-off ratio of  $10^7$ , and a subthreshold swing (SS) of  $\sim 150 \text{ mV Dec}^{-1}$ averaged over four orders of magnitude at  $V_{\rm DS} = 0.2$  V. The ohmic contact behaviour was confirmed via the transfer length method as shown in Fig. S7<sup>†</sup> and the specific contact resistivity  $(\rho_{\rm C})$  is extracted to be around 0.13  $\Omega$  cm<sup>2</sup>. It is the high contact resistivity that contributes to the low source-to-drain current  $(I_{\rm DS})$  ~210 nA at  $V_{\rm DS}$  = 1.0 V when no gate bias was applied. The gate leakage current density is determined to be lower than  $10^{-6}$ A cm<sup>-2</sup> and the corresponding breakdown voltage is around 4.8 V, suggesting the deposited Al<sub>2</sub>O<sub>3</sub> layer is of good insulating quality over the gate-to-source voltage  $(V_{GS})$  measurement range (Fig. S8b<sup>†</sup>). Fig. 1d illustrates the collected output  $(I_{DS}-V_{DS})$ curves as a function of  $V_{GS}$ , where current saturation and pinchoff are visualized. We noticed that the spacing of output  $(I_{DS} V_{\rm DS}$ ) curves measured at  $V_{\rm GS} = +2.0$  V is sub-linear, indicating the possible effect of self-heating. To extract the effective mobility of TiO<sub>2</sub> thin film, we have also presented the transfer curve at  $V_{\rm DS} = 100$  mV in Fig. S8d<sup>†</sup> and the estimated electron mobility is 3.87 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, comparable to the as-far best-reported value (~10.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>).<sup>25</sup>

### 3.2 Temperature-dependent electrical characterization

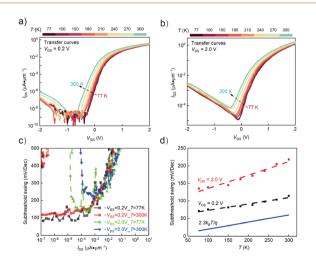

To further elucidate the charge transport process of TiO<sub>2</sub> TFTs, we have performed the transfer characteristics at different temperatures ranging from 300 K to 77 K at an interval of 30 K. Fig. 2a and b demonstrate the temperature-dependent subthreshold behaviour measured at  $V_{\rm DS} = 0.2$  V and 2.0 V, respectively. As can be seen, the collected transfer curves become steeper and the corresponding turn-on voltages shift to more positive values when the temperature cools down. In addition, the on-off ratio shows insensitive temperature dependence, which suggests that our proposed TiO<sub>2</sub> TFTs can operate at quite broad temperature ranges. Fig. 2c presents the extracted temperature-dependent SS plotted against  $I_{DS}$ . The averaged SS extracted over four orders of magnitude decreases from 150 mV  $\text{Dec}^{-1}$  at T = 300 K to 100 mV  $\text{Dec}^{-1}$  when the temperature cools to 77 K ( $V_{DS} = 0.2$  V). The charge transport mechanism for our TiO2 TFTs is dominated by thermionic emission, therefore, the extracted SS should be linear as a function of temperature.<sup>28,29</sup> Fig. 2d illustrates the extracted minimum SS plotted against temperature, where the experimentally measured SS scales linearly as a function of temperature as expected and shares a similar slope to the theoretical values following the Boltzmann limitation. Detailed temperature-dependent SS analysis is discussed in ESI Section 9.†

**Fig. 2** Temperature-dependent transistor performance. (a and b) Subthreshold behaviour measured at various temperatures ranging from 77 K to 300 K while the  $V_{\rm DS}$  remains constant at 0.2 V and 2.0 V, respectively. (c) SS plotted against  $I_{\rm DS}$  at the lowest and highest temperatures ( $V_{\rm DS} = 0.2$  V and 2.0 V). (d) Extracted minimum SS as a function of temperature. The red and black dotted curves represent the experimentally measured values, while the blue line refers to the theoretical value following the Boltzmann limitation (2.3  $k_{\rm B}T/q$ ).

#### 3.3 Dynamic switching response and transient performance

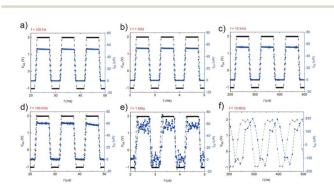

To explore the time-resolved dynamic switching characteristics of TiO<sub>2</sub> TFTs, transient time traces of source to drain current  $(I_{\rm DS})$  were analyzed by applying pulsed gate voltages ( $V_{\rm GS}$  from -1.0 V to +2.0 V) at constant  $V_{\rm DS} = +2.0$  V. Fig. 3a-f displays different dynamic responses of TiO2 TFTs collected at frequencies ranging from 100 Hz to 10 MHz at a step of one order. To begin with, we observed noise-free and stable currents  $(I_{\rm DS})$  being switched on and off at frequencies below 1.0 MHz. The on and off states of  $I_{DS}$  agree well with the previous DC result. Subsequently, Fig. 3e shows that  $I_{DS}$  can still be switched on and off, but the noise level of  $I_{DS}$  becomes significant at a frequency of 1.0 MHz. The reason may be due to the shorter collection time of each cycle at higher frequencies (the noise level increases significantly when the collection averaging time decreases, especially when the averaging time is shorter than 1 μs). Furthermore, the switching rise time and fall time can be defined as the time elapse when the switched-on current decays from 90% to 10% and vice versa in the transient time trace.<sup>30,31</sup> Since the rise time and fall time are both around 100 ns, the maximum switching speed is calculated to be around 5.0 MHz via the following equation

$$f_{\rm max} = 1/(\tau_{\rm Rise} + \tau_{\rm Fall})$$

Finally, the device cannot be switched on and off consistently when the applied frequency exceeds 10 MHz (Fig. 3f) probably due to the response time of the device itself or the limitation of our electrical setup (the collection time should be longer than 10 ns and the noise level becomes significant when the frequency is above 10 MHz). Thus, it requires more effort and higher-speed measurement equipment to estimate the accurate response time in our future work. Notably, our proposed TiO<sub>2</sub> TFTs can be switched on and off even at a temperature as low as 77 K (Fig. S10†). The dynamic switching response and transient performance of TiO<sub>2</sub> TFTs switch on more opportunities for high-speed electronic devices based on metal oxide TFTs.

Fig. 3 Dynamic switching behaviour of TiO<sub>2</sub> TFTs. Transient time traces collected at various frequencies by applying pulsed gate voltages ( $V_{\rm GS}$  from -1.0 V to +2.0 V) at constant  $V_{\rm DS}$  = +2.0 V. (a-f) represent the corresponding time traces collected at different frequencies from 100 Hz to 10 MHz at an interval of one order of magnitude.

### 3.4 Static and dynamic resistive-loaded inverter characteristics

To further explore the potential application of TiO<sub>2</sub> TFTs on high-speed circuits, we have constructed a resistive-loaded inverter and studied the static and dynamic transient behaviour. Fig. 4a shows clear voltage transfer curves collected at various resistive loads ranging from 100 k $\Omega$  to 1.0 M $\Omega$ . The inset illustrates the circuit design with a fixed supply voltage ( $V_{DD} =$ 2.0 V). We observed that the output voltages  $(V_{out})$  can be "pulled down" to near 0 V as the load resistor increases to 1.0 M\Omega. Fig. 4b displays the voltage transfer characteristics as a function  $V_{DD}$ , where stable and consistent inverting behaviour can be observed at different supply voltages ranging from 0.2 V to 3.0 V. Fig. 4c illustrates the corresponding gain curves, which exhibit a maximum voltage gain of  $\sim$ 4.8 at  $V_{\rm DD}$  = 3.0 V. Notably, the maximum voltage gain shows an insensitive dependence on temperature ranging from 77 K to 300 K, which suggests that the resistive-loaded inverter can operate at a quite broad regime (Fig. 4d). Our proposed TiO<sub>2</sub> TFTs may find potential applications as quantum computing components and active backplane matrix operated at cryogenic temperatures. The last section is the dynamic performance of the resistive-loaded inverter, which

Fig. 4 Static and dynamic resistive-loaded inverter characteristics. (a) Voltage transfer curves are collected at different resistive loads while the supply voltage remains constant ( $V_{DD} = 2.0$  V). The inset presents the circuit design and electrical connection. (b) Voltage transfer curves as a function of  $V_{DD}$  and the resistive load is 1.0 M $\Omega$ . (c) Calculated gain curves at different  $V_{DD}$  levels ranging from 0.2 V to 3.0 V. (d) Temperature-dependent voltage transfer curves and related gain curves at  $V_{DD} = 3.0$  V and load = 1.0 M $\Omega$ . Dynamic behaviour of resistive-loaded inverter in response to square-waveform input signals with a frequency of 100 Hz (e) and 10 kHz (f). The amplitude of input signals is 4.0 V with a 50% duty cycle and the supply voltage is constant at 2.0 V while the resistive load is 1.0 M $\Omega$ .

View Article Online Paper

was evaluated by applying square-waveform input signals with an amplitude of 4.0 V, a 50% duty cycle, no offset voltage, and various frequencies. To visualize the transient behavior, the external resistive load was fixed at 1.0 MΩ. Meanwhile, the fastswitching time traces of output electrical signals were collected and visualized by a digital bench oscilloscope. Fig. 4e and f demonstrate the transient behaviour in response to squarewaveform input signals with a frequency of 100 Hz and 10 kHz, respectively. A stable and consistent inverting performance can be observed at different frequencies. In addition, the rise  $(t_r)$  and fall time  $(t_f)$  of switching events in Fig. 4f can be fitted by simple exponential functions to estimate the inverter response time.<sup>17,32</sup> Both the rise and fall time are calculated to be around 5 ms, thus, the maximum speed of the resistiveloaded inverter is no more than 100 kHz. However, it is noteworthy that this maximum speed is not limited by the device itself but by the resistive-capacitive time constant (RC delay) of the constructed circuit. Table S1<sup>†</sup> benchmarks the electrical performances and highlights the differences between our proposed TiO<sub>2</sub> TFTs and other types of devices. Our work studies systematically the static DC performance, dynamic switching behaviour, and logic gates of resistive-loaded inverters, which paves the way towards forthcoming highspeed and low voltage-driven electronic components based on metal semiconductors.

## 4. Conclusions

In summary, we have presented low voltage-driven, highperformance  $TiO_2$  thin film transistors, which can be operated at a switching speed of MHz. The static DC performance and dynamic switching behaviour of the proposed  $TiO_2$  TFTs are studied systematically. The film quality and thickness of the prepared  $TiO_2$  thin film were investigated *via* XRD, Raman, XPS, AFM, and ellipsometry techniques. Our work shows that there is still plenty of room to explore and improve the switching frequencies of metal oxide thin film transistors, which may find their future application in the next generation of display backplanes and high-speed electronic circuits.

## Author contributions

Xiaoping Chen: conceptualization, investigation, formal analysis, methodology, visualization, writing – original draft, writing – review & editing. Jiancong Ni: resources, formal analysis. Weiqiang Yang: investigation, formal analysis. Shaoying Ke: supervision, resources, formal analysis, writing – review & editing. Maosheng Zhang: supervision, resources, conceptualization, formal analysis, writing – review & editing.

# Conflicts of interest

There are no conflicts to declare.

The authors are grateful to the President's Fund of Minnan Normal University (KJ2021005 and KJ2023002). X. Chen thanks the support under the Natural Science Foundation of Fujian Province, China (Grant No. 2022J05173). S. Ke thanks the support under the National Natural Science Foundation of China under Grant No. 62004087.

### References

- 1 K. Myny, Nat. Electron., 2018, 1, 30-39.

- 2 C. D. Dimitrakopoulos and D. J. Mascaro, *IBM J. Res. Dev.*, 2001, **45**, 11–27.

- 3 K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano and H. Hosono, *Nature*, 2004, **432**, 488–492.

- 4 M. J. Powell, *IEEE Trans. Electron Devices*, 1989, **36**, 2753–2763.

- 5 A. Nathan, A. Kumar, K. Sakariya, P. Servati, S. Sambandan and D. Striakhilev, *IEEE J. Solid-State Circuits*, 2004, **39**, 1477–1486.

- 6 S. D. Brotherton, Semicond. Sci. Technol., 1995, 10, 721.

- 7 R. A. Street, T. N. Ng, R. A. Lujan, I. Son, M. Smith, S. Kim, T. Lee, Y. Moon and S. Cho, *ACS Appl. Mater. Interfaces*, 2014, 6, 4428–4437.

- 8 Z. Chai, S. A. Abbasi and A. A. Busnaina, *ACS Appl. Electron. Mater.*, 2023, **5**, 2328–2337.

- 9 H. Hosono, Nat. Electron., 2018, 1, 428.

- 10 W. Xu, L. Hu, C. Zhao, L. Zhang, D. Zhu, P. Cao, W. Liu, S. Han, X. Liu, F. Jia, Y. Zeng and Y. Lu, *Appl. Surf. Sci.*, 2018, 455, 554–560.

- 11 A. Abliz, L. Xu, D. Wan, H. Duan, J. Wang, C. Wang, S. Luo and C. Liu, *Appl. Surf. Sci.*, 2019, 475, 565–570.

- 12 J. Zhang, M. Jia, M. G. Sales, Y. Zhao, G. Lin, P. Cui, C. Santiwipharat, C. Ni, S. McDonnell and Y. Zeng, ACS Appl. Electron. Mater., 2021, 3, 5483–5495.

- 13 N. Zhong, J. J. Cao, H. Shima and H. Akinaga, *IEEE Electron Device Lett.*, 2012, **33**, 1009–1011.

- 14 J. W. Park, S. W. Han, N. Jeon, J. Jang and S. Yoo, *IEEE Electron Device Lett.*, 2008, **29**, 1319–1321.

- 15 Z. Ying, C. Feng, Z. Zhao, S. Dhar, H. Dalir, J. Gu, Y. Cheng, R. Soref, D. Z. Pan and R. T. Chen, *Nat. Commun.*, 2020, **11**, 2154.

- 16 A. F. Paterson and T. D. Anthopoulos, *Nat. Commun.*, 2018, 9, 5264.

- 17 J. W. Borchert, U. Zschieschang, F. Letzkus, M. Giorgio, R. T. Weitz, M. Caironi, J. N. Burghartz, S. Ludwigs and H. Klauk, *Sci. Adv.*, 2020, 6, eaaz5156.

- 18 F. Wang, Y. Liu, T. X. Hoang, H.-S. Chu, S.-J. Chua and C. A. Nijhuis, *Small*, 2022, 18, 2105684.

- 19 F. Wang, T. X. Hoang, H.-S. Chu and C. A. Nijhuis, *Laser Photonics Rev.*, 2022, **16**, 2100419.

- 20 X. Liu, K. Pan, Z. Zhang and Z. Feng, *Appl. Surf. Sci.*, 2023, **640**, 158337.

- 21 G. Luka, B. S. Witkowski, L. Wachnicki, M. Andrzejczuk, M. Lewandowska and M. Godlewski, *CrystEngComm*, 2013, 15, 9949–9954.

- 22 A. T. Hassan, E. S. Hassan and O. M. Abdulmunem, *J. Mech. Behav. Mater.*, 2021, **30**, 304–308.

- 23 J. Zhang, P. Cui, G. Lin, Y. Zhang, M. G. Sales, M. Jia, Z. Li, C. Goodwin, T. Beebe, L. Gundlach, C. Ni, S. McDonnell and Y. Zeng, *Appl. Phys. Express*, 2019, 12, 096502.

- 24 B. Kim, T. Kang, G. Lee and H. Jeon, *Nanotechnology*, 2022, 33, 045705.

- 25 W. S. Shih, S. J. Young, L. W. Ji, W. Water and H. W. Shiu, *J. Electrochem. Soc.*, 2011, **158**, H609.

- 26 Y. Xu, S. Wu, P. Wan, J. Sun and Z. D. Hood, *RSC Adv.*, 2017, 7, 32461–32467.

- 27 B. Bharti, S. Kumar, H. N. Lee and R. Kumar, *Sci. Rep.*, 2016, 6, 32355.

- 28 M. Nadeem, I. Di Bernardo, X. Wang, M. S. Fuhrer and D. Culcer, *Nano Lett.*, 2021, 21, 3155–3161.

- 29 S. Datta, W. Chakraborty and M. Radosavljevic, *Science*, 2022, **378**, 733–740.

- 30 M. Naqi, Y. Cho and S. Kim, ACS Appl. Electron. Mater., 2023, 5, 3378–3383.

- 31 H.-D. Kim, M. Naqi, S. C. Jang, J.-M. Park, Y. C. Park, K. Park, H.-H. Nahm, S. Kim and H.-S. Kim, ACS Appl. Mater. Interfaces, 2022, 14, 13490–13498.

- 32 T. Haldar, T. Wollandt, J. Weis, U. Zschieschang, H. Klauk, R. T. Weitz, J. N. Burghartz and M. Geiger, *Sci. Adv.*, 2023, **9**, eadd3669.