# Journal of Materials Chemistry C

Accepted Manuscript

This is an *Accepted Manuscript*, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about *Accepted Manuscripts* in the **Information for Authors**.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the <u>Ethical guidelines</u> still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this *Accepted Manuscript* or any consequences arising from the use of any information it contains.

Cite this: DOI: 10.1039/c0xx00000x

**ARTICLE**

www.rsc.org/xxxxxx

# High-Performance, Low-Temperature Solution Processed Amorphous Indium Oxide Thin-Film Transistors Using a Volatile Nitrate Precursor

Chang-Ho Choi, Seung-Yeol Han, Superstraint and Chih-hung Chang\*a

5 Received (in XXX, XXX) Xth XXXXXXXXX 20XX, Accepted Xth XXXXXXXXX 20XX DOI: 10.1039/b000000x

In this study, we fabricated amorphous indium oxide thin film transistors (TFTs) on the display glass at various annealing temperature from 200 °C to 300 °C. Using a volatile nitrate precursor, we were able to fabricate TFTs with excellent device performance within this annealing temperature range. Amorphous 10 In<sub>2</sub>O<sub>3</sub> films could be obtained by carefully controlling film thickness and annealing temperature. TFTs based on amorphous  $In_2O_3$  channel layers with an average mobility as high as 7.5 cm<sup>2</sup>/Vs,  $I_{on}/I_{off}$  ratio of  $10^7$ , and  $V_{on}$  = -5 V could be fabricated at 300 °C annealing temperature in air. The devices prepared at 200 °C still exhibits transistor characteristics with an average mobility of 0.04 cm<sup>2</sup>/Vs, I<sub>on</sub>/I<sub>off</sub> ratio of 10<sup>5</sup>, and V<sub>on</sub>= 0 V. The temperature effects on the device performances are elucidated based on the X-ray 15 photoelectron spectroscopy and thermal gravimetric analysis characterization results of precursors and the resulting amorphous In<sub>2</sub>O<sub>3</sub> thin films.

#### Introduction

Metal oxide semiconductors have been intensively researched over several decades due to their unique electrical and optical 20 characteristics. 1-3 Metal oxide semiconductors cover a wide range of optical band gap, exhibiting high optical transparency. In conjunction with high optical transparency, the high field effect mobility and excellent thermal/environmental durability make them promising alternative materials to replace hydrogenated 25 amorphous silicon and organic semiconductors as active channels for thin-film transistors (TFTs).4, 5 In terms of manufacturing metal oxide semiconductors as the active channel layers in TFTs, gas-phase deposition technique that requires a vacuum such as sputtering has been primarily employed, which involves high 30 capital and operation cost. Recently, metal oxide TFTs fabricated via solution-based processes have been pursued considerably for their potentials of offering simplicity, low cost, high throughput, and large area deposition. 6-12 Among various solution-based process, the use of metal salt precursor is probably the most 35 commonly used technique to fabricate metal oxide thin film transistors because of simplicity and its ability to accurately control film composition<sup>7, 8</sup>. In the metal salt precursor approach, solution precursors dissolved in solvent are printed or spun onto substrates followed by an annealing process. The precursor films 40 would transform to metal oxide thin films via absorption, reaction and desorption processes. 13 Annealing conditions are very important in terms of determining device performances. The annealing temperature should be high enough to decompose and desorb all by-products and to convert metal-hydroxide-metal into

45 metal-oxide-metal framework. 8 In addition, the annealing process also control the oxygen vacancy formation which will influence the conductivity of metal oxide semiconductor film.

The high annealing temperature is considered a major obstacle to the application of solution-processed metal oxide 50 semiconductors on flexible plastic substrate. Significant efforts have been made to fabricate metal oxide TFTs using low temperature process without sacrificing device performances. Kim et al. reported various metal oxide TFTs with good device performances at low temperature annealing condition using 55 combustion processing. 14 Combustion fuels such as acetylacetone and urea were used to reduce the thermal energy required to remove organic impurities and convert the precursor film into the oxide framework. In<sub>2</sub>O<sub>3</sub> semiconductor annealed at temperature as low as 200 °C produced TFTs with a mobility value of 0.81 60 cm<sup>2</sup>/Vs on 300 nm SiO<sub>2</sub> dielectric layer and 13 cm<sup>2</sup>/Vs on amorphous aluminium oxide dielectric layer. Banger et al. reported a 'sol-gel on chip' process in which a controlled amount of water vapour was used to activate hydrolysis and condensation reaction of as spun metal alkoxide samples during the annealing 65 process. 15 Han et el. reported In<sub>2</sub>O<sub>3</sub> TFTs with high device performances at a temperature range from 200 to 300 °C, which was achieved in O<sub>2</sub>/O<sub>3</sub> atmosphere annealing condition. <sup>16</sup> TFTs annealed in O<sub>2</sub>/O<sub>3</sub> atmosphere were found to possess more oxygen vacancy formation with less hydroxyl groups compared 70 to those fabricated in air atmosphere. High field effect mobility of 22.14 cm<sup>2</sup>/Vs was achieved using this process at 300 °C on oxidized silicon wafer. Another novel annealing process using photochemical activation of sol-gel films at room temperature

was recently reported by Kim el al. 17 They used deep-ultraviolet light to fabricate amorphous metal oxide TFTs without imposing the intended thermal heating. The photo-annealing enabled the fabrication of In<sub>2</sub>O<sub>3</sub> TFTs with a maximum average mobility of 5 3.6 cm<sup>2</sup>/Vs, 11.29 cm<sup>2</sup>/Vs on oxidized silicon wafer and on Al<sub>2</sub>O<sub>3</sub> dielectric layer deposited by atomic layer deposition on glass.

In<sub>2</sub>O<sub>3</sub> semiconductor has the potential to be an excellent channel layer for TFTs due to its high mobility of 10-75 cm<sup>2</sup>/Vs, transparency and chemical stability. One challenge of In<sub>2</sub>O<sub>3</sub> as a 10 channel layer is the transition to polycrystalline thin film at a relatively low annealing temperature. 18 Polycrystalline films have grain boundaries, increasing potential barrier for the charge transport and creating a uniformity issue for large area applications. 19, 20 The other issue of In<sub>2</sub>O<sub>3</sub> is its high conductivity 15 which could prevent TFTs from functioning well as an electrical switch. To resolve the abovementioned challenges zinc, gallium, or both elements has been doped into hosting In<sub>2</sub>O<sub>3</sub>. <sup>20-25</sup> Such dopants not only disrupt the formation of long-range order of In<sub>2</sub>O<sub>3</sub> films, but also suppress the formation of oxygen vacancies 20 reducing electron density. The addition of zinc and gallium normally requires higher annealing temperatures to achieve the same level of field effect mobility as undoped indium oxide film from a solution-based process. In this regard, it is desirable to produce amorphous In<sub>2</sub>O<sub>3</sub> TFTs without using dopants while 25 maintaining excellent electrical characteristics of In<sub>2</sub>O<sub>3</sub>. <sup>26</sup>

Most of high performance, solution-processed indium oxide TFTs reported in the literature have been fabricated on heavilydoped Si substrates using thermally grown gate oxide. In terms of manufacturing metal oxide TFTs for near-term commercial 30 production, studies of metal oxide TFTs fabricated on display glass substrate using readily available dielectric layers are necessary. Electrical performances based on SiO<sub>2</sub> dielectric layer grown on display glass substrate generally fall short of those prepared with thermally grown SiO<sub>2</sub> dielectric layer on heavily-35 doped Si substrate. 27-30 Here we report amorphous In<sub>2</sub>O<sub>3</sub> TFTs with CVD grown SiO<sub>2</sub> dielectric layer on display glass substrate. By using a volatile nitrate precursor with an optimal film thickness, we can fabricate amorphous In<sub>2</sub>O<sub>3</sub> TFTs at relatively low temperatures, ranging from 200 to 300°C. Excellent device 40 performances were obtained, with an average mobility as high as 7.5 cm<sup>2</sup>/Vs,  $I_{on}/I_{off}$  ratio of  $10^7$ , and  $V_{on}=-5$  V from amorphous indium oxide channel layers fabricated at 300 °C annealing temperature in air. The devices prepared at 200 °C still exhibits transistor characteristics with an average mobility of 0.04 cm<sup>2</sup>/Vs, 45  $I_{on}/I_{off}$  ratio of 10<sup>5</sup>, and  $V_{on}=0$  V.

# **Experimental**

# **Device fabrication**

Molybdenum (Mo) layer with 200 nm thickness was formed 50 onto display glass substrate for a gate electrode by using a sputter deposition, and then deposition of SiO<sub>2</sub> dielectric layer with 100 nm thickness was performed by PECVD process. The breakdown voltage of the PECVD SiO<sub>2</sub> dielectric layer was measured to be greater than 15 MV/cm at 1 MV/cm. The leakage current of the 55 dielectric layer at 1MV/cm was also measured to be 4.5 nA/cm<sup>2</sup>. The capacitance of the dielectric layer was measured to be 191

nF/cm<sup>2</sup> at 1 kHz, resulting in the permittivity of 5.1. The substrates were treated using O2 plasma cleaning prior to the deposition. In (NO<sub>3</sub>)<sub>3</sub> anhydrous salt and 2-methoxyethanol 60 solvent was purchased from Alfa Aesar and Fisher Scientific respectively and used without further purification process. 0.05 M In(NO<sub>3</sub>)<sub>3</sub> was dissolved in 2-methoxyethanol solvent and spincoated with 4500 RPM for 30 seconds. As-deposited film was dried on a hot plate at 120 °C for 30 minutes to evaporate solvent. 65 The film was then annealed at targeted temperature in air condition for 2 hours. In<sub>2</sub>O<sub>3</sub> films were patterned by a photolithography process. The patterned samples were dried on a hot plate at 120 °C prior to the deposition of Al source and drain. The source and drain were deposited by thermal evaporation 70 using a shadow mask for patterning. The active channel layer was defined with 1200 µm and 200 µm for width and length, respectively.

#### Characterization

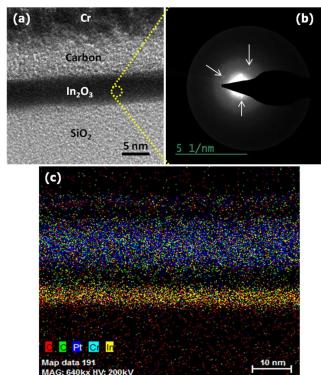

Device characterization was performed in ambient condition using Agilent Technologies E5270B Semiconductor Parameter Analyzer. The morphology and roughness of the films were analysed using atomic force microscope (AFM, Veeco Nanoscope digital instruments). The optical properties of the 80 films were studied using UV-vis spectroscopy (Jasco, V-670 Spectrophotometer). For the transmittance measurement, In<sub>2</sub>O<sub>3</sub> film was deposited on bare soda lime glass substrate. X-ray diffraction (XRD, Bruker D8 discover) was used to study the crystallinity of the films. X-ray photoelectron spectroscopy (XPS, 85 ESCALAB 200-IXL instrument with Mg K radiation) was employed to investigate elemental composition of the films. Thermal gravimetric analysis (TGA) was used to investigate the thermal responses of the metal salt precursor films (TA Q600). High resolution transmission electron microscopy (HRTEM, FEI <sub>90</sub> TITAN 80-200) equipped with electron dispersive spectroscopy (EDS) and convergent beam electron diffraction (CBED) was used to measure the thickness, composition, and crystallinity of the film. For the preparation of HRTEM specimen of the In<sub>2</sub>O<sub>3</sub> film, a focus ion beam (FIB) process was employed. Both 95 chromium and carbon layer were deposited during the FIB process to protect the In<sub>2</sub>O<sub>3</sub> film.

#### Results and Discussion

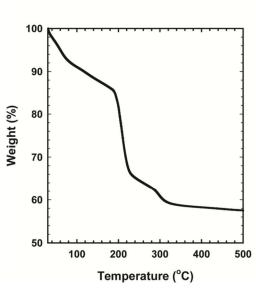

Thermal responses of various metal salt precursors with 100 different anions have been studied.<sup>29, 31</sup> It was found that nitrate anion requires less thermal energy to decompose completely as compared to other anions such as acetate, and chloride. TGA curve showing the decomposition of the precursor prepared from indium nitrate dissolved in 2-methoxyethanol as a function of 105 temperature is given in Figure 1. The initial weight loss starting from room temperature till 200 °C is attributed to the evaporation of adsorbed or chemisorbed water and solvent. Significant weight loss was observed between 200 °C and 300 °C, and the thermal decomposition of indium nitrate was complete around 300 °C. 110 The TGA analysis indicates the possibility of converting indium nitrate precursor into indium oxide allowing the fabrication of TFT below 300°C.

Fig.1. Thermal gravimetric analysis of indium nitrate precursor.

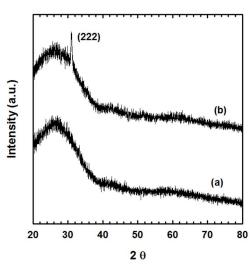

Based on the TGA results, we attempted to fabricate In<sub>2</sub>O<sub>3</sub> TFTs using indium nitrate precursor at various annealing 5 temperatures, ranging from 200 °C to 300 °C. Figure 2a displays cross sectional TEM view of the In<sub>2</sub>O<sub>3</sub> film after annealed at 300 °C. A uniform film with approximately 6 nm could be seen in the TEM image. Elemental mapping based on EDS analysis suggests that indium and oxygen atoms are uniformly dispersed 10 within the film (Figure 2c). CBED was performed to examine the crystallinity of the film. The film appears to be consisted of mostly amorphous phase. Some small diffraction spots could also be observed from the CBED image (Figure 2b). The percentage of crystalline phase in the film was estimated to be less than 10 % 15 after analysing the CBED data using a Gatan digital micrograph software. XRD spectrum of the film was obtained to confirm the amorphous phase (Figure 3a). No peak was observed, indicating the film is primarily composed of amorphous indium oxide. In<sub>2</sub>O<sub>3</sub> is generally known to readily crystallize in a cubic structure even 20 at low process temperature although amorphous In<sub>2</sub>O<sub>3</sub> were also reported. 11, 16, 18, 32-34 Hsieh et al. reported the transition of crystal phase of ZnO TFTs which is dependent on thickness of the ZnO film.<sup>35</sup> As the thickness is below 40 nm, the ZnO film has the amorphous phase, but the thickness over 40 nm the film started to 25 become crystalline. Other materials have also shown a similar thickness dependence of crystallinity. 36-38 As mentioned previously, the thickness of our In<sub>2</sub>O<sub>3</sub> film is about 6 nm, which is far thinner than the reported amorphous ZnO film. We repeated the deposition process three times to increase the thickness of 30 In<sub>2</sub>O<sub>3</sub> film and observed the transition of crystallinity from amorphous phase to crystalline (Figure 3 b). The peak at  $\theta$ =31.5° corresponds to (222) plane in cubic In<sub>2</sub>O<sub>3</sub> (JCPDS, No. 65-3170). During the annealing process of as-deposited In<sub>2</sub>O<sub>3</sub> film, the film on the fringes of the SiO<sub>2</sub> layer tends to form amorphous phase 35 rather than crystalline because the amorphous In<sub>2</sub>O<sub>3</sub> film prefers to relax in the same phase of the amorphous SiO2 layer, resulting in less interface strain.<sup>35, 38</sup> Since our interest is placed on the amorphous In<sub>2</sub>O<sub>3</sub>, we prepared amorphous In<sub>2</sub>O<sub>3</sub> thin films for TFT fabrication and performed more detailed 40 characterizations of the films.

Fig.2. Amorphous In<sub>2</sub>O<sub>3</sub> thin film: (a) HRTEM image, (b) CBED image (white arrows present diffraction), (c) EDS elemental map.

Fig.3. XRD pattern of In<sub>2</sub>O<sub>3</sub> film prepared (a) by one-time spin coating (~6nm)and (b) by three-time spin coating process.

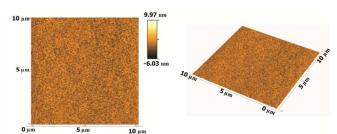

Figure 4 shows the AFM image of the amorphous In<sub>2</sub>O<sub>3</sub> thin film. The average roughness was measured to be 1.2 nm, indicating that the film is relatively smooth without forming particles. The 50 surface roughness of the film is one of important parameters in determining the electrical performance of the device.<sup>39, 40</sup> Since the rough surface is more likely to create interface trap state density, smoother film is required to improve the electrical performance of devices. The AFM image shows no grains, 55 further confirming the amorphous phase of In<sub>2</sub>O<sub>3</sub> film.

Fig.4. AFM image of In<sub>2</sub>O<sub>3</sub> thin film.

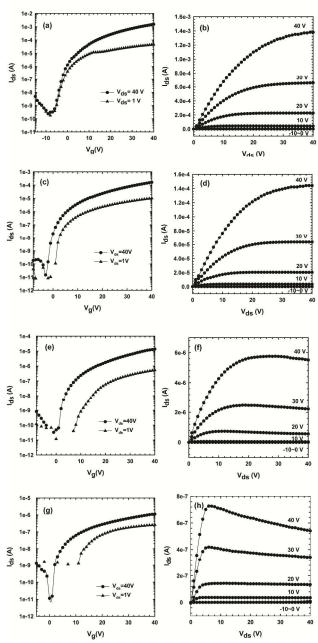

Fig.5. Transfer and output characteristic curves of In<sub>2</sub>O<sub>3</sub> TFTs 5 prepared at (a, b) 300 °C, (c, d) 280 °C, (e, f) 250 °C, and (g, h) 200 °C.

Amorphous In<sub>2</sub>O<sub>3</sub> TFTs were fabricated with a bottom gate and top contact structure, and the device performance was measured. The In<sub>2</sub>O<sub>3</sub> films annealed at 200 °C, 250 °C, 280 °C, and 300 °C in air were used as the active channel layer for TFTs. Figure 5

10 displays the representative transfer characteristics  $(I_{ds}-V_g)$  and output characteristic (I<sub>ds</sub>-V<sub>ds</sub>) curves of TFTs prepared at each annealing temperature. All of the devices show n-type enhanced mode transistor characteristics. The devices also exhibit the excellent saturation. At V<sub>ds</sub>=40 V, the transfer characteristic 15 curves indicate low off current and a high  $I_{on}/I_{off}$  ratio of  $10^6 \sim 10^7$ , except for the device annealed at 200 °C which shows a Ion/Ioff ratio of 10<sup>5</sup>. A turn-on voltage (V<sub>on</sub>) of the device annealed at 300 °C is approximately -8 V, and as the annealing temperature decreases the Von value moves close to 0 V. The trends of the 20 device performances at V<sub>ds</sub>=1 V are similar to those observed at V<sub>ds</sub>=40 V. On-current is approximately one order of magnitude lower as  $V_{ds}$  decreases from 40V to 1V, and consequently  $I_{on}/I_{off}$ ratio also decreases. At 200 °C annealing temperature, a turn-on voltage and I<sub>on</sub>/I<sub>off</sub> ratio are significantly deviated upon V<sub>ds</sub> values. 25 Summary of electrical performances of the devices prepared at various annealing temperatures is listed in Table 1.

There are several models to extract the mobility of TFTs. While each model has its characteristics in extracting the mobility, we adopted a field effect mobility model which is commonly  $_{\rm 30}$  used and obtained  $\,$  by transconductance at low  $V_{\rm ds},^{1,\,41}$

The model to extract the field effect mobility is following.

$$\mu_{\rm FE} = \frac{g_m}{C_i \frac{W}{L} V_{ds}}$$

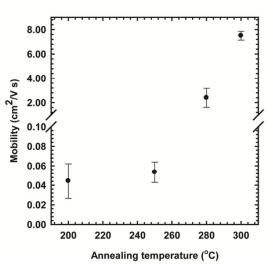

Where g<sub>m</sub> is transconductance, C<sub>i</sub> is capacitance of gate insulator layer, W and L is width and length of channel respectively, and  $V_{ds}$  is the applied drain voltage. In this study, drain voltage of  $V_{ds}$ <sub>35</sub> =1 V was applied for the field effect mobility extraction. Field effect mobility values were averaged by measuring device performances of at least 30 devices prepared at each annealing temperature. Average field effect mobility values of the device prepared at different annealing condition are presented in Figure 40 6. The highest average mobility of 7.5 cm<sup>2</sup>/Vs was obtained at 300 °C with a relatively small variation. The average mobility falls off to 2.8 cm<sup>2</sup>/Vs at 280 °C. At 250 °C annealing condition, the average mobility significantly decreases to 0.05 cm<sup>2</sup>/Vs. The lowest average mobility of 0.04 cm<sup>2</sup>/Vs was measured from the 45 devices that were annealed at 200 °C. As annealing temperature decreases, the average mobility value decreases along with an increase of the deviation of mobility values.

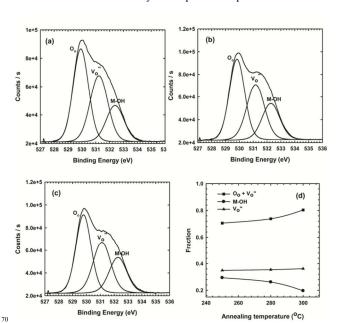

In order to investigate the device performances with respect to the annealing temperature, XPS O 1s spectrums of indium oxide 50 films obtained at different annealing temperature are shown in Figure 7a~c. XPS O 1s spectrums of all devices can be deconvoluted into three peaks. The peak located at 529.9 eV corresponds to the oxygen in the oxide lattice having six nearest indium atoms without oxygen vacancy. 16, 42 The peak at 531.2 eV 55 is assigned to the oxygen in within the indium-oxygen cluster with oxygen vacancies.<sup>25</sup> The peak at 532.4 eV arises from In-OH oxygen atoms. 42 The fractions constituting the each oxygen lattice were estimated on the basis of the area integration of each oxygen peak (Figure 7d). The fraction analysis of each oxygen 60 component indicates that the composition of the In<sub>2</sub>O<sub>3</sub> film is susceptible to the annealing temperature. As the annealing temperature decreases from 300 °C to 250 °C, the fraction of oxide decreases while the fraction of hydroxide increases. Since thermally driven condensation reaction converts hydroxide into 65 oxide, high temperature annealing is favourable in completing the

oxide formation. The device performance is considerably associated with the extent of oxide formation according to the material design concept for metal oxide TFTs introduced by Hosono and co-workers.<sup>4, 43</sup> They proposed that metal oxides 5 composed of heavy metal cations with a (n-1)d<sup>10</sup>s<sup>0</sup> (n>4) form spatial spreading ns orbitals in the conduction band minimum (CBM) which serve as the charge carrier path. Therefore, oxide formation is a prerequisite condition to achieve the high performance devices. In addition to the formation of In-O-In 10 framework, the formation of oxygen vacancies plays an important role in determining the electrical performances of devices. Oxygen vacancies, formed during the thermal annealing process, constitutes the shallow electron donor level close to the CBM and provide charge carriers.<sup>44</sup> The concentration of charge 15 carriers strongly depends on the annealing condition, and optimal process condition should be identified to manufacture the devices that exhibit high mobility, decent  $I_{on}/I_{off}$  ratio and  $V_{on}$ . If the concentration of charge carriers exceeds a certain level, the device suffers from a low I<sub>on</sub>/I<sub>off</sub> ratio or even could not be turned 20 off properly. In contrast, the device with low level of oxygen vacancies will show lower filed effect mobility. In our amorphous In<sub>2</sub>O<sub>3</sub> TFTs, the annealing temperature range from 200 °C to 300 °C appears to be suitable to fabricate functional TFTs. According to the XPS spectrum, the fraction of oxygen vacancies 25 slightly increases with an increase of the annealing temperature. This result is consistent with previously reported results.<sup>25, 31, 45</sup> Given a high level of oxide formation for charge carrier path and oxygen vacancies for charge carrier creation, the device annealed at 300 °C attains a high average mobility value of 7.5 cm<sup>2</sup>/ Vs. 30 We increased the annealing temperature up to 500 °C to further study the relation between annealing temperature and oxygen vacancy formation. The amorphous film was still obtained even in the high annealing temperature, but the device is highly conductive and unable to be switched off, reflecting an excessive

35 level of oxygen vacancy formation.

Fig. 6. Summary of average mobility of devices prepared at various annealing temperature.

The temperature effect on the variation of mobility values can

be discussed based on the TGA data and XPS spectra It was found that the mobility variation is magnified as the annealing temperature decreases. This result is closely related to the thermal decomposition of the as-deposited In<sub>2</sub>O<sub>3</sub> film. All of impurities 45 including solvent molecules, hydroxide, and anions are expected to be thermally decomposed at annealing temperatures higher than 300 °C according to the TGA data (Figure 1). In contrast, impurities are more likely to remain in the films that were annealed at a temperature below 300 °C. This causes the 50 attenuation of device performance and the mobility variation to a large extent. These impurities also seem to affect the device performance. At the annealing temperature of 250 °C and 200 °C, I<sub>ds</sub> value decreases with increasing V<sub>ds</sub>, which is not observed at high annealing temperature of 280 °C and 300 °C (Figure 5f and 55 h). In particular, degree of the current decrease is more significant at 200 °C where much more impurities remain in the channel layer. It has been known that the device stability is considerably associated with impurities. 46, 47 In our devices, the instability is caused by incomplete thermal decomposition of indium 60 precursors, leaving organic impurities in the channel layer. 48 The overall device performances of the devices prepared at various annealing temperatures are summarized in Table 1.

Vygranenko et al. fabricated In<sub>2</sub>O<sub>3</sub> channel layer by reactive ion beam assisted evaporation at room temperature with PECVD 65 SiO<sub>2</sub> gate dielectric. 49 The devices show a field effect mobility of 33 cm<sup>2</sup>/Vs along with an I<sub>on</sub>/I<sub>off</sub> ratio of 10<sup>9</sup>. Although the overall device performances are superior to those of our In<sub>2</sub>O<sub>3</sub> TFTs, it is worth noting that our In2O3 TFTs with the decent field effect mobilities were fabricated by a cheap solution process.

Fig.7. XPS O 1s spectra of In<sub>2</sub>O<sub>3</sub> thin films prepared at various annealing temperatures: (a) 300 °C, (b) 280 °C, (c) 250 °C, and (d) fraction analysis of oxygen component as a function of annealing temperature.

Table 1. Summary of electrical performances of amorphous In<sub>2</sub>O<sub>3</sub> TFTs

| Temperature (°C) | Average mobility (cm <sup>2</sup> / Vs) | $I_{on}/I_{off}$ | $V_{on}\left( V\right)$ |

|------------------|-----------------------------------------|------------------|-------------------------|

| 300              | 7.5                                     | $10^{6\sim7}$    | -10~-5                  |

| 280              | 2.4                                     | $10^{6\sim7}$    | -4~-2                   |

| 250              | 0.05                                    | $10^{6\sim7}$    | 0~4                     |

| 200              | 0.04                                    | $10^{4\sim5}$    | 0~1                     |

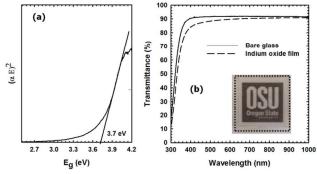

Figure 8 displays the optical properties of  $In_2O_3$  thin film prepared at 300 °C. The optical band gap of the film was measured to be around 3.7 eV, which is wide enough to manufacture optical transparent devices. The transmittance spectrum of the film clearly shows its high optical transparency reaching 90 % transmittance over the visible wavelength.

Fig.8. Optical properties of In<sub>2</sub>O<sub>3</sub> thin film prepared at 300 °C: (a) band gap estimation and (b) transmittance spectrum.

### **Conclusions**

Amorphous In<sub>2</sub>O<sub>3</sub> TFTs were fabricated on the display glass via a metal salt precursor approach using a volatile indium nitrate precursor solution. Taking the advantage of a volatile nitrate precursor, the TFTs with high device performances were achieved using low annealing temperatures. The devices with an average mobility of 7.5 cm<sup>2</sup>/Vs, I<sub>on</sub>/I<sub>off</sub> ratio of 10<sup>7</sup>, and V<sub>on</sub> = -5 V were fabricated successfully using a 300 °C annealing process. <sup>20</sup> By properly control the film thickness, thin films that are consisted of primarily amorphous indium oxide were obtained, which is more favourable for large scale device fabrication. This study demonstrates that feasibility of fabricating amorphous indium oxide TFTs on display glass with excellent electrical <sup>25</sup> performance using an annealing temperature that is compatible with the display manufacturing process.

### **Notes and references**

- <sup>a</sup> Oregon Process Innovation Center/Microproduct Breakthrough Institute and School of Chemical, Biological & Environmental Engineering,

- 30 Oregon State University, Corvallis, OR 97331. United States. Fax: 541-737-4600; Tel: 541-737-8548;

- E-mail: Chih-hung.Chang@oregonstate.edu

- <sup>b</sup> CSD Nano, Inc., Corvallis, OR 97330. United States.

- <sup>c</sup> Department of Materials Science and Engineering, National Chiao Tung

- 35 University, 1001 Ta Hsueh Road, Hsinchu 30050, Taiwan

- <sup>d</sup> AU Optronics Corporation, No.1, Li-Shin Rd., Hsinchu Science Park, Hsinchu, Taiwan

- ‡ Footnotes should appear here. These might include comments relevant to but not central to the matter under discussion, limited experimental and spectral data, and crystallographic data.

- E. Fortunato, P. Barquinha and R. Martins, Advanced Materials, 2012, 24, 2945-2986.

- 45 2. J.-Y. Kwon, D.-J. Lee and K.-B. Kim, *Electronic Materials Letters*, 2011, 7, 1-11.

- 3. US Patent No. 8679587, C.-h. Chang, D. Lee and Y.-J. Chang, 2014, p. 25.

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano and H. Hosono, *Nature*, 2004, 432, 488-492.

- E. M. C. Fortunato, P. M. C. Barquinha, A. Pimentel, A. M. F. Goncalves, A. J. S. Marques, L. M. N. Pereira and R. F. P. Martins, *Advanced Materials*, 2005, 17, 590-594.

- S. Jeong and J. Moon, Journal of Materials Chemistry, 2012, 22, 1243-1250.

- D.-H. Lee, S.-Y. Han, G. S. Herman and C.-H. Chang, *Journal of Materials Chemistry*, 2009, 19, 3135-3137.

- 8. D.-H. Lee, Y.-J. Chang, G. S. Herman and C.-H. Chang, *Advanced Materials*, 2007, **19**, 843-847.

- 60 9. G. Adamopoulos, A. Bashir, S. Thomas, W. P. Gillin, S. Georgakopoulos, M. Shkunov, M. A. Baklar, N. Stingelin, R. C. Maher, L. F. Cohen, D. D. C. Bradley and T. D. Anthopoulos, *Advanced Materials*, 2010, 22, 4764-4769.

- C. Avis and J. Jang, *Journal of Materials Chemistry*, 2011, 21, 65 10649-10652.

- H. S. Kim, P. D. Byrne, A. Facchetti and T. J. Marks, *Journal of the American Chemical Society*, 2008, 130, 12580-12581.

- 12. M.-G. Kim, H. S. Kim, Y.-G. Ha, J. He, M. G. Kanatzidis, A. Facchetti and T. J. Marks, *Journal of the American Chemical Society*, 2010, **132**, 10352-10364.

- 13. S.-Y. Han, D.-H. Lee, G. S. Herman and C.-H. Chang, *Journal of Display Technology*, 2009, **5**, 520-524.

- M.-G. Kim, M. G. Kanatzidis, A. Facchetti and T. J. Marks, *Nature Materials*, 2011, 10, 382-388.

- 75 15. K. K. Banger, Y. Yamashita, K. Mori, R. L. Peterson, T. Leedham, J. Rickard and H. Sirringhaus, *Nature Materials*, 2011, 10, 45-50.

- 16. S.-Y. Han, G. S. Herman and C.-h. Chang, *Journal of the American Chemical Society*, 2011, **133**, 5166-5169.

- 17. Y.-H. Kim, J.-S. Heo, T.-H. Kim, S. Park, M.-H. Yoon, J. Kim, M. S. Oh, G.-R. Yi, Y.-Y. Noh and S. K. Park, *Nature*, 2012, **489**, 128-132.

- J. R. Bellingham, W. A. Phillips and C. J. Adkins, *Thin Solid Films*, 1991, 195, 23-31.

- 19. H. Nakazawa, Y. Ito, E. Matsumoto, K. Adachi, N. Aoki and Y. Ochiai, *Journal of Applied Physics*, 2006, **100**, 093706.

- K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano and H. Hosono, Japanese Journal of Applied Physics Part 1-Regular Papers Brief Communications & Review Papers, 2006, 45, 4303-4308.

- 90 21. P. K. Nayak, M. N. Hedhili, D. Cha and H. N. Alshareef, Acs Applied Materials & Interfaces, 2013, 5, 3587-3590.

- P. K. Nayak, T. Busani, E. Elamurugu, P. Barquinha, R. Martins, Y. Hong and E. Fortunato, *Applied Physics Letters*, 2010, 97, 183504.

- S.-J. Seo, C. G. Choi, Y. H. Hwang and B.-S. Bae, *Journal of Physics D-Applied Physics*, 2009, 42, 035106.

- 24. C.-G. Lee and A. Dodabalapur, Applied Physics Letters, 2010, 96, 243501.

- 25. S. Jeong, Y.-G. Ha, J. Moon, A. Facchetti and T. J. Marks, Advanced Materials, 2010, 22, 1346-1350.

- 5 26. Dhananjay and C.-W. Chu, Applied Physics Letters, 2007, 91, 132111.

- 27. K. Song, D. Kim, X.-S. Li, T. Jun, Y. Jeong and J. Moon, Journal of Materials Chemistry, 2009, 19, 8881-8886.

- 28. H. C. Cheng, C. F. Chen and C. C. Lee, Thin Solid Films, 2006, 498,

- 29. W. H. Jeong, J. H. Bae and H. J. Kim, Ieee Electron Device Letters, 2012, 33, 68-70.

- 30. D. Kim, C. Y. Koo, K. Song, Y. Jeong and J. Moon, Applied Physics Letters, 2009, 95, 103501.

- 15 31. S. Jeong, J.-Y. Lee, S. S. Lee, Y. Choi and B.-H. Ryu, Journal of Physical Chemistry C, 2011, 115, 11773-11780.

- 32. Dhananjay, S.-S. Cheng, C.-Y. Yang, C.-W. Ou, Y.-C. Chuang, M. C. Wu and C.-W. Chu, Journal of Physics D-Applied Physics, 2008, 41, 092006.

- 20 33. J. R. Bellingham, W. A. Phillips and C. J. Adkins, Journal of Physics-Condensed Matter, 1990, 2, 6207-6221.

- 34. B. G. Lewis and D. C. Paine, Mrs Bulletin, 2000, 25, 22-27.

- 35. H.-H. Hsieh and C.-C. Wu, Applied Physics Letters, 2007, 91, 013502.

- 25 36. I. C. Cheng, S. Allen and S. Wagner, Journal of Non-Crystalline Solids, 2004, 338, 720-724.

- 37. J. Bailat, E. Vallat-Sauvain, A. Vallat and A. Shah, Journal of Non-Crystalline Solids, 2004, 338, 32-36.

- 38. K. S. Ahn, Y. C. Nah and Y. E. Sung, Journal of Vacuum Science & Technology a-Vacuum Surfaces and Films, 2002, 20, 1468-

- 39. A. B. Y. Chan, C. T. Nguyen, P. K. Ko, S. T. H. Chan and S. S. Wong, Ieee Transactions on Electron Devices, 1997, 44, 455-

- 35 40. J. Raja, K. Jang, N. Hong Hanh, T. Thanh Thuy, W. Choi and J. Yi, Current Applied Physics, 2013, 13, 246-251.

- 41. R. L. Hoffman, Journal of Applied Physics, 2004, 95, 5813-5819.

- 42. P. K. Nayak, M. N. Hedhili, D. Cha and H. N. Alshareef, Applied Physics Letters, 2013, 103, 033518.

- 40 43. H. Hosono, N. Kikuchi, N. Ueda and H. Kawazoe, Journal of Non-Crystalline Solids, 1996, 200, 165-169.

- 44. H. Hartnagel, A. Dawar, A. Jain and C. Jagadish, Semiconducting Transparent Thin Films, IOP Publishing, Bristol, 1995.

- 45. T. Jun, K. Song, Y. Jeong, K. Woo, D. Kim, C. Bae and J. Moon, Journal of Materials Chemistry, 2011, 21, 1102-1108.

- 46. W. R. Mateker, J. D. Douglas, C. Cabanetos, I. T. Sachs-Quintana, J. A. Bartelt, E. T. Hoke, A. El Labban, P. M. Beaujuge, J. M. J. Frechet and M. D. McGehee, Energy & Environmental Science, 2013, 6, 2529-2537.

- 50 47. D. Knipp, A. Benor, V. Wagner and T. Muck, Journal of Applied Physics, 2007, 101, 044504.

- 48. Y. Vygranenko, K. Wang and A. Nathan, Applied Physics Letters, 2007, 91, 263508.

- 49. Y. Vygranenko, K. Wang, R. Chaji, M. Vieira, J. Robertson and A. Nathan, Thin Solid Films, 2009, 517, 6341-6344. 55