## Materials Advances

**View Article Online**

View Journal | View Issue

## PAPER

Check for updates

Cite this: *Mater. Adv.*, 2024, 5, 5998

Received 31st January 2024, Accepted 2nd June 2024

DOI: 10.1039/d4ma00095a

rsc.li/materials-advances

## Introduction

In the field of thermoelectricity, silicon nanostructures have emerged as promising alternatives to conventional thermoelectric materials (*e.g.*, Bi, Sb, Te, and Pb alloys) due to silicon's abundance, non-toxic nature, and compatibility with CMOS technology.<sup>1–9</sup> However, silicon's inefficiency as a thermoelectric material stems from its high thermal conductivity of 150 W m<sup>-1</sup> K<sup>-1</sup>,<sup>10</sup> in contrast to bismuth telluride alloys with a thermal conductivity approximately one hundred times lower (~1.5 W m<sup>-1</sup> K<sup>-1</sup>).<sup>11</sup> The dimensionless figure of merit (*zT*), a crucial metric for thermoelectric efficiency, is approximately 1 for Bi<sub>2</sub>Te<sub>3</sub> at room temperature<sup>12</sup> and drops below 0.001 for bulk silicon.<sup>13</sup> At temperature *T*, *zT* is defined as

$$zT = S^2 \sigma T/\kappa \tag{1}$$

where *S*,  $\sigma$ , and  $\kappa$  denote the Seebeck coefficient, electrical conductivity, and thermal conductivity, respectively. The thermal conductivity is expressed as the sum of two components: lattice or phononic thermal conductivity ( $\kappa_{\rm Ph}$ ), and electronic thermal

# Thermoelectric characterization of crystalline nano-patterned silicon membranes<sup>†</sup>

Hafsa Ikzibane, 跑 <sup>a</sup> Akash Patil, <sup>ab</sup> Jon Canosa, <sup>a</sup> Etienne Okada, <sup>a</sup> Etienne Blandre, <sup>a</sup> Emmanuel Dubois<sup>a</sup> and Jean-François Robillard\*<sup>a</sup>

Research towards efficient and environmentally friendly thermoelectrics proposes silicon nanostructures as possible candidates through reduction of the phononic thermal conductivity. However, there is scarce literature about experimental measurements of the thermoelectric figure-of-merit *zT* on actual crystalline silicon devices. This article reports on the fabrication and full thermoelectric characterization of crystalline 60 nm thick membranes. To that end, an experiment with four types of built-in devices was designed using a silicon-on-insulator substrate to extract the Seebeck coefficient, electrical conductivity and thermal conductivity. The results show indeed a reduced thermal conductivity of 31 W m<sup>-1</sup> K<sup>-1</sup> for a 60 nm thick Si membrane and  $\kappa = 18$  W m<sup>-1</sup> K<sup>-1</sup> for a porous Si membrane. This reflects an 88% reduction in thermal conductivity compared to the bulk Si material and a 42% reduction compared to plain Si membranes. In terms of power generation, the power factor of the fabricated devices surpasses that of state-of-the-art silicon thin films at room temperature. Notably, a *zT* figure of merit of 0.04 is reported for a 60 nm thick phonon-engineered Si membrane, which is considerably higher than that of bulk Si(0.001) but lower than previously reported results on other types of nano-objects.

conductivity ( $\kappa_e$ ). The latter one is owing to heat transfer by free charge carriers through the structure. The phononic contribution, evaluated in the diffusive regime, is expressed as

$$\kappa_{\rm ph} = \frac{C_{\rm P} \times L_{\rm Ph} \times v}{3} \tag{2}$$

where  $\kappa_{\rm Ph}$  is the lattice thermal conductivity related to the heat propagation through the lattice vibrations (phonons) depending on mean free path  $L_{\rm Ph}$ , sound velocity  $\nu$  and specific heat  $C_{\rm P}$ .

The literature reports methods to enhance the thermoelectric figure of merit (*zT*) for silicon by increasing the ratio of electrical conductivity to thermal conductivity ( $\sigma/\kappa$ ). This involves diminishing thermal conductivity ( $\kappa$ ) by minimizing the impact of phonon-mediated heat transport ( $\kappa_{\rm Ph}$ ), a dominant factor in semiconductors.<sup>14</sup> The reduction of  $\kappa_{\rm Ph}$  can be accomplished by diminishing the mean free path of phonons through diffusion *via* artificial defects and boundaries. This approach can be achieved by employing nanometric structures like thin membranes<sup>15–22</sup> or nanowires (NW),<sup>23–25</sup> surface roughening,<sup>26,27</sup> surface oxidization,<sup>28,29</sup> and so-called phonon engineering methods.<sup>30–38</sup> Arguably, some of the reported synthesis methods, such as nanosphere lithography, or objects, such as nanowires, are unlikely to be transferred into a mass production infrastructure.

The characterization of such nanostructures involves additional complexity compared to bulk measurements. Especially, heat flux evaluation is delicate since many parasitic leakage channels are involved and non-negligible at the nanoscale.

<sup>&</sup>lt;sup>a</sup> Univ. Lille, CNRS, Centrale Lille, Junia, Univ. Polytechnique Hauts-de-France, UMR 8520 – IEMN – Institut d'Electronique de Microélectronique et de Nanotechnologie, F-59000 Lille, France

<sup>&</sup>lt;sup>b</sup> STMicroelectronics – 850 rue jean Monnet 38920 Crolles, France

<sup>†</sup> Electronic supplementary information (ESI) available. See DOI: https://doi.org/ 10.1039/d4ma00095a

#### Paper

Furthermore, the fabrication processes sometimes involve aggressive etching steps that can deteriorate the crystallinity of samples. This work aims at tackling the lack of experimental measurements for the thermoelectric figure of merit (zT) in crystalline silicon nanostructures assembled in CMOS compatible devices.

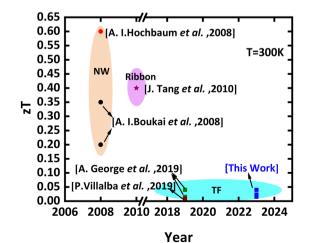

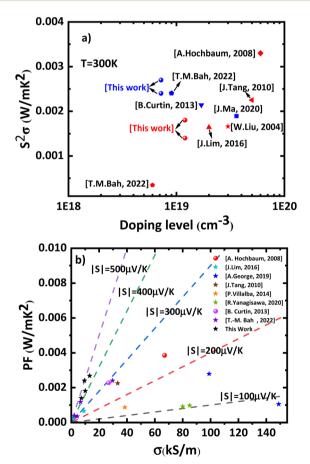

In this study, we focus on the fabrication and characterization of devices designed to assess thermoelectric (TE) properties, including the thermal conductivity, Seebeck coefficient, and electrical conductivity of crystalline silicon membranes. Our investigation involves both plain (P) and phononic engineered (PE) silicon membranes, integrated into a planar configuration on the same chip. A novel Seebeck measurement method employing a thermometry technique is introduced. The subsequent section details the fabrication process and characterization methodology, presenting the power factor (PF) and zT for both P and PE membranes. A comparative analysis is provided, highlighting the comparison with the state of the art (Fig. 1).

## Fabrication and characterization

#### Design and fabrication

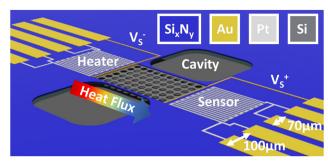

The Seebeck coefficient is a critical parameter for evaluating the efficiency of a thermoelectric material. To measure the Seebeck coefficient of silicon (Si) we designed a suspended micro-thermoelectric membrane schemed on Fig. 2. The technique employs resistive thermometry to measure the temperature difference along the Si membrane. Two serpentine platinum wires are used either as Joule heaters or resistive sensors. They are positioned near the edges of the membrane to ensure precise measurement of the temperature difference. The crystalline silicon membrane is fully suspended and is connected at both ends with gold metallic pads. These contact enable the measurement of Seebeck voltage resulting from temperature gradients.

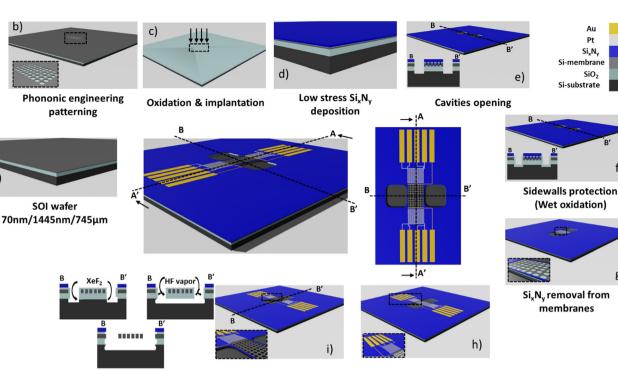

The devices are made from silicon on insulator (SOI) substrates using processes compatible with the complementary

Fig. 1 Reported values of zT for crystalline nanostructure silicon planar configurations.

### View Article Online Materials Advances

Fig. 2 Seebeck coefficient measurement device

metal-oxide-semiconductor (CMOS) technology, as depicted in Fig. 3. The process builds upon prior efforts aimed at reducing the thermal conductivity of silicon through a combination of silicon thinning and the creation of pore lattices.<sup>1,31,39</sup> The starting point is an SOI wafer featuring a 70 nm thick active layer, a 145 nm thick buried oxide (BOX) layer and a 745 µm silicon handler. (a) High-resolution e-beam lithography and Cl<sub>2</sub>/Ar reactive ion etching (RIE) are then employed to define the pore patterns (b), creating a square lattice of 46 nm diameter pores with a pitch of 100 nm, as illustrated in Fig. 4(d). The selection of these dimensions represents a compromise between technological constraints, minimizing pitch and neck size, and enhancing porosity. This approach aims at maximising the impact of pores towards lower thermal conductivity.40,41 Subsequently, the silicon is doped using either p-boron or n-phosphorus ion implantation, targeting a concentration of 10<sup>19</sup> cm<sup>-3</sup> (c). Then, a low-stress nonstoichiometric silicon nitride layer  $(Si_xN_y)$  is deposited (d) isolating the membrane from the central platinum resistive heater. Silicon nitride serves the dual purpose of insulating the membrane electrically and enhancing the mechanical robustness of the structures. Cavities are then etched around the membranes to create apertures for subsequent suspension (e).  $Si_xN_y$  is removed from the silicon membranes to facilitate the flow of electric current while preventing the formation of a parallel thermal conduction channel in silicon nitride (Si<sub>x</sub>N<sub>y</sub>).

Metallic sensors and leads are formed through platinum and gold evaporation (h). Before metallization, a thermal oxide layer is grown on the Si membranes to protect the sidewalls from vapor phase xenon-difluoride (XeF<sub>2</sub>) etching (f). This final step in the device fabrication process involves suspending the silicon membranes using XeF<sub>2</sub> and HF vapor etching to ensure their thermal insulation from the rest of the SOI substrate. The device features 10 pads for providing heating power, and measuring temperature difference and the Seebeck voltage. Samples were fabricated at lengths of 20  $\mu$ m, 60  $\mu$ m, 100  $\mu$ m and 140  $\mu$ m; each length is individually fabricated three times with widths of 10  $\mu$ m, 20  $\mu$ m and 30  $\mu$ m. This leads to a total number of 12 geometries in both P and PE versions for each doping type (n-type and p-type) as detailed in the ESI.†

#### Seebeck coefficient

The devices were characterized using a thermometry technique, involving the determination of temperature difference based on

Paper

f)

g)

b)

Fig. 3 Seebeck coefficient measurement device fabrication steps

XeF2 & vapor HF etching

C

(a) Seebeck coefficient measurement device illustrating the Au Fig. 4 pads connected to the heater/sensor and the 20  $\mu m$   $\times$  20  $\mu m$  Si membrane, (b) Close-up view of the suspended Si membrane and the Pt heater/sensor. (c) Top close-up view of the suspended PE Si membrane. (d) Details of the pore patterns on the Si membrane. (e) Cross-section view of the holes.

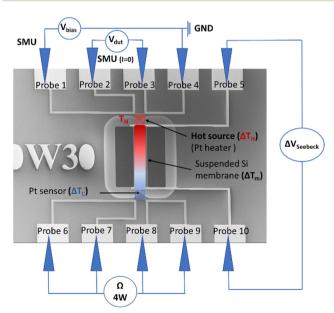

the electrical resistance variation of the metal. The characterization process has two main steps. Firstly, the Pt heater serpentine is calibrated on a controlled heating chuck to extract the temperature coefficient of resistance (TCR), denoted as  $\alpha$ . Secondly, the Pt heater is biased with a variable voltage. Based on the known  $\alpha$ , the increase in electrical resistance due to the voltage variation is converted into temperature. In this case, the Pt film, which is 20 nm thin, exhibits a temperature coefficient of resistance  $\alpha = 2.49 \times 10^{-3} \text{ K}^{-1} \pm 2\%$ . Fig. 5 illustrates the measurement protocol employed for determining the Seebeck coefficient.

The measurements are conducted using a face-to-face configuration with five probes. In this setup, the first probe is connected to the Keysight/Agilent E5281B SMU module, which

applies a bias to the Pt heater. The second and third probes are connected to the Keysight/Agilent E5281A ATTO level highresolution SMU module, enabling the measurement of the voltage across the Pt heater using a zero current source as a high impedance voltmeter. The fourth probe is connected to the ground. For the Pt sensor, the four probes (probe 6, 7, 8, and 9) are connected to an Agilent 34461A four-wire ohmmeter,

Pt & Au metallization

Fig. 5 Experimental setup for Seebeck coefficient measurement characterization

#### Paper

allowing the measurement of the sensor's resistance. Additionally, an ammeter (Agilent 34401 A) is connected in series with the Agilent 34461A four-wire ohmmeter to control the injected current. By adjusting the calibration measurement range, very low current  $(1-2 \mu A)$  can be injected to avoid the self-heating via the Joule effect in the Pt sensor. Finally, the remaining two probes (probes 5 and 10), which are linked to the membrane, are connected to a Keysight/Agilent 34461A voltmeter. In the following,  $\Delta T_{\rm H} = T_{\rm H} - T_0$  denotes the temperature difference between the hot side  $T_{\rm H}$  compared to the reference temperature  $T_0$  of the silicon substrate. Similarly, we obtain  $\Delta T_{\rm C} = T_{\rm C} - T_{\rm 0}$ . This setup allows the sensing of the voltage ( $\Delta V_{\text{Seebeck}}$ ) generated by the temperature difference across the membrane ( $\Delta T_{\rm m} = \Delta T_{\rm H} - \Delta T_{\rm C}$ ). The Pt heater electrical resistance at various temperatures was determined using IC-CAP software which calculates the derivative of the voltage with respect to current, while the electrical resistance of the Pt sensor and the Seebeck voltage ( $\Delta V_{\text{Seebeck}}$ ) were directly measured using the connected instruments.

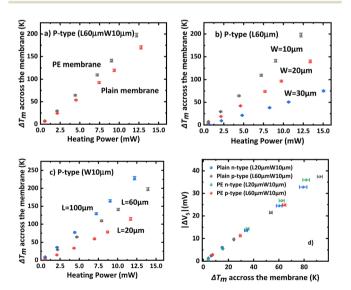

Fig. 6(a) presents the temperature difference along the membrane  $\Delta T_{\rm m}$ . Notably, PE membranes demonstrate a higher temperature difference for a given heating power, indicating enhanced thermal gradient management or decreased thermal conductance across the membrane, as expected. Additionally, the temperature difference exhibits an increase with membrane length and a decrease with membrane width (Fig. 6b and c). The rise in thermal gradient with length can be attributed to the extended heat conduction pathway within the membrane. With an increased membrane length, heat traverses a longer distance, resulting in a larger temperature difference across the membrane. Conversely, the reduction in thermal gradient with width can be explained by the augmented cross-sectional area available for heat conduction. In Fig. 6d, the Seebeck voltage is

**Fig. 6** Temperature difference across p-type silicon as a function of heating power for (a) P and PE membranes with dimensions 60  $\mu$ m in length and 10  $\mu$ m in width, (b) PE membranes with a fixed length of 60  $\mu$ m and varying widths, and (c) PE membranes with a fixed width of 10  $\mu$ m and varying lengths. (d) Absolute measured Seebeck voltage as a function of the temperature difference across different Si membranes.

plotted against the membrane's temperature difference  $(\Delta T_{\rm m})$ . At  $\Delta T_{\rm m} < 40$  K, both PE and P membranes exhibit similar slopes. However, at higher  $\Delta T_{\rm m}$ , a noticeable divergence occurs, emphasizing the dependence of the Seebeck coefficient with material properties and temperature rather than reflecting the geometric arrangement.

Transient thermo-reflectance (TTR) was employed to validate the results obtained through the electrical measurements.

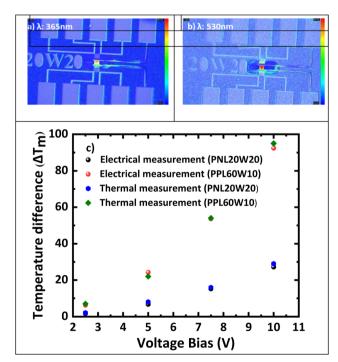

Fig. 7 illustrates thermal transient reflectance (TTR) images of an n-type Si plain membrane with dimensions ( $L = 20 \mu m$ ,  $W = 20 \mu m$ ) subjected to a voltage bias of 7.5 V. The figure presents two scenarios: (a) employing a 530 nm wavelength with a Pt coefficient of thermal reflectance of  $1.2 \times 10^{-4} \text{ K}^{-1}$  for the determination of  $\Delta T_{\rm H}$  and  $\Delta T_{\rm C}$ , and (b) utilizing a 365 nm wavelength with a Si CTR of  $1.37 \times 10^{-4} \text{ K}^{-1}$  for the determination of  $\Delta T_{\rm m}$ . The temperature difference ( $\Delta T_{\rm m}$ ) observed across the suspended plain Si membrane through both electrical and thermal measurements are nearly identical (Fig. 7d), validating the accuracy of the previously determined Seebeck coefficient.

#### Thermal conductivity

To quantify thermal conductivity, we used the single-laser Raman thermometry technique. This technique uses the temperaturedependent peak position in silicon<sup>42</sup> to measure the local hot spot temperature rise  $\Delta T$  originating from the excitation laser absorption. By using variable density, the intensity of the excitation laser

**Fig. 7** Thermal transient reflectance (TTR) images of n-type Si plain membranes ( $L = 20 \ \mu$ m,  $W = 20 \ \mu$ m) under a 7.5 V voltage bias, with (a) employing a 365 nm wavelength and Pt coefficient of thermal reflectance (CTR) of  $1.2 \times 10^{-4} \ K^{-1}$ , and (b) using a 365 nm wavelength with Si CTR of  $1.37 \times 10^{-4} \ K^{-1}$ . (c) Temperature difference as a function of voltage bias for plain; n-type (PNL20W20) and p-type (PPL60W10) membranes: comparison of electrical and thermal measurement techniques.

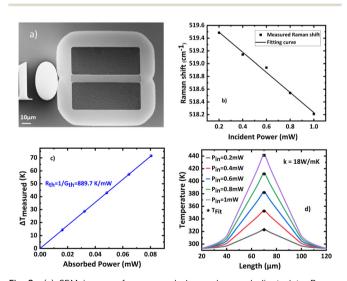

can be varied, thus allowing the absorbed power  $P_{\rm abs}$  to be tuned. It is then possible to measure the sample thermal conductance  $G_{\rm th} = P_{\rm abs}/\Delta T$ . Finally, the thermal conductivity of the layer of interest must be de-embedded from the thermal conductance through modeling. It is thus useful to have the simplest sample geometry, and to make sure that the heat flow will be forced through the material of interest. For these reasons, additional membranes without electrodes are designed on the same substrate (Fig. 8a) and the sample is placed in a thermally regulated vacuum stage (Linkam HFS350-PB4) equipped with an optical window. We refer the reader to reported implementations of Raman thermometry<sup>43-45</sup> and give more details about the setup used in the ESI† section.

In our case, the laser is focused at the center of the membrane with a 50×/NA0.42 long-distance objective. The waist of the focused spot was measured to be 1.48 µm using the knife-edge method. Fig. 8b shows the silicon Raman diffusion peak position as a function of the absorbed power. The latter is obtained as  $P_{\rm in} \times A$ , where  $P_{\rm in}$  is the measured incident power and A is the absorbance of the membranes calculated using the rigorous coupled wave analysis code RETICOLO.<sup>46</sup> Making use of the reported coefficient  $\partial \omega / \partial T = -0.02 \text{ cm}^{-1} \text{ K}^{-142}$  the shift of the Raman diffusion peak is converted into a temperature rise on Fig. 8c and  $G_{\rm th}$  is obtained. Eventually, in order to extract the thermal conductivity  $\kappa$ , the membrane and its surrounding frame is modelled using the finite element software COMSOL. Si<sub>x</sub>N<sub>y</sub>, buried oxide and silicon wafer thermal conductivities are assumed to be 1.55, 1.5 and 148 W m<sup>-1</sup> K<sup>-1</sup> respectively. The Gaussian laser

**Fig. 8** (a) SEM image of a suspended membrane dedicated to Raman measurements. (b) Variation of Raman shift as a function of the incident power of a p-type plain membrane, t = 60 nm, L = 20 µm, W = 10 µm. (c) The experimental temperature difference across the p-type membrane with t = 60 nm, L = 60 µm and W = 10 µm as a function of the absorbed power (A = 8.05%). (d) p-type Si phononic membrane for parameterized power of the laser light incident into the middle of the membrane,  $\kappa = 18 \text{ W m}^{-1} \text{ K}^{-1}$ , absorption A = 10.9%, hole's diameter 45.8 nm and pitch = 100 nm. Black points are  $\mu$ TR experimental values. Membrane has the thickness t = 60 nm, L = 60 µm and W = 10 µm. Wing size of the device geometry equals 20 µm.

source is modelled, and the stationary heat equation heat equation solved with  $\kappa$  as a parameter. Fig. 8d shows the temperature profiles obtained for each incident power value. The results show excellent agreement of the central temperature with the measurement by making use of a single thermal conductivity value. The agreement can be obtained within a  $\pm 1$  W m<sup>-1</sup> K<sup>-1</sup> range.

## Results & discussion

#### Seebeck coefficient

The Seebeck coefficients (S) for plain p-type, phonon engineered p-type, plain n-type, and phonon engineered n-type membranes were found to be 424  $\mu$ V K<sup>-1</sup>, 440  $\mu$ V K<sup>-1</sup>,  $-451 \text{ }\mu\text{V} \text{ }\text{K}^{-1}$ , and  $-504 \text{ }\mu\text{V} \text{ }\text{K}^{-1}$ , respectively. In a degenerate semiconductor, the total Seebeck coefficient  $(S_{tot})$  is influenced by two specific components: the diffusive contribution  $(S_e)$  and the phonon drag contribution  $(S_{ph})$ . The diffusive contribution originates from the migration of charge carriers in response to temperature gradients, while the phonon drag contribution arises from the exchange of momentum between the nonequilibrium phonon populations and the charge carriers. Previous studies by Geballe<sup>47</sup> and Sadhu<sup>48</sup> highlighted the significance of S<sub>ph</sub> in bulk Si at room temperature. Examining the impact of the phonon drag effect on the Seebeck coefficient in ultrathin SOI layers, F. Salleh et al.49 demonstrated its noteworthy influence near room temperature, particularly in the lightly doped region ( $N_{\rm D}$  < 10<sup>19</sup> cm<sup>-3</sup>, where  $N_{\rm D}$  is the doping level). Furthermore, H. Ikeda et al.<sup>50</sup> emphasized that the impurity band density of state (DOS) distribution primarily governs the Seebeck coefficient in heavily doped regions. The doping levels for plain p-type and n-type 60 nm membranes were measured to be 1.2  $\times$  10  $^{19}~cm^{-3}$  and 7.2  $\times$  10  $^{18}~cm^{-3}$ , respectively. Correspondingly, their electrical conductivity values were measured at 100.8 S cm and 131.8 S cm, respectively. The diffusive contribution  $(S_e)$  for plain p-type and n-type membranes is calculated using eqn (3) and amounts to 182  $\mu$ V K<sup>-1</sup> and -263  $\mu$ V K<sup>-1</sup> respectively.

$$S_{e}^{n}(T) = -\frac{k_{B}}{q} \times \left[3/2 + \ln\left(\frac{N_{C}(T)}{n(T)}\right)\right]$$

$$S_{e}^{p}(T) = \frac{k_{B}}{q} \times \left[3/2 + \ln\left(\frac{N_{V}(T)}{p(T)}\right)\right]$$

$$n(T) = \frac{N_{D}}{2} + \sqrt{\frac{N_{D}^{2}}{4} + n_{t}^{2}(T)}$$

$$p(T) = \frac{N_{A}}{2} + \sqrt{\frac{N_{A}^{2}}{4} + n_{t}^{2}(T)}$$

$$n_{i}(T) = \sqrt{N_{C}(T) \cdot N_{V}(T)} \cdot \exp\left(-\frac{E_{G}(T)}{2 \cdot k_{B} \cdot T}\right)$$

(3)

where  $k_{\rm B}$  is the Boltzmann constant (1.38 × 10<sup>-23</sup> J K<sup>-1</sup>), *q* the elementary charge (1.602 × 10<sup>-19</sup> C), *h* the Planck constant (6.62 × 10<sup>-34</sup> m<sup>2</sup> kg s<sup>-1</sup>), *p*(*T*) and *n*(*T*) are the hole and electron volume densities respectively.  $N_{\rm V}(T)$  and  $N_{\rm C}(T)$  denote the

The phonon drag contribution  $(S_{\rm ph})$  is determined as 242 µV K<sup>-1</sup> and -188 µV K<sup>-1</sup> for plain p-type and n-type membranes, respectively. The calculation is based on the subtraction of the diffusive contribution  $(S_{\rm e})$  from the total Seebeck coefficient  $(S_{\rm tot})$ .  $S_{\rm ph}$  represent 41% of the  $S_{\rm tot}$  of n-type membrane. Thus, we can confirm that the phonon-drag contribution at room temperature in 60 nm thin crystalline silicon is nonnegligible. It is however commonly admitted that this effect should disappear in nanometric systems owing to the suppression of long mean-free path phonons. A temperature-dependent study of the phonon-drag Seebeck component, though beyond the scope of this study, will hopefully shed light on this finding.

#### Thermal conductivity

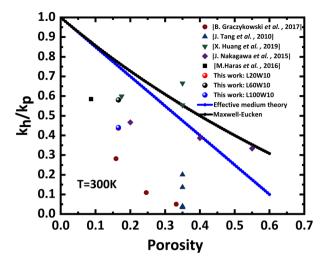

Incorporating patterns into the membrane design results in a notable decrease in thermal conductivity, with a reduction of about 56% observed for membranes with lengths of 20 µm and 100 µm, and a reduction of 42% for membranes with a length of 60 µm. This decrease can be attributed to several factors. Firstly, the introduction of patterns creates additional interfaces and boundaries within the membrane. These interfaces act as scattering sites for heat-carrying phonons, impeding their efficient propagation and resulting in a decrease in overall thermal conductivity. This can be also understood as a modification of the phonon mean free paths distribution towards lower values.<sup>51</sup> Fig. 9 illustrates the relationship between the thermal conductivity ratio of the phononic membrane ( $\kappa_{\rm h}$ ) to the thermal conductivity of the plain membrane ( $\kappa_{\rm P}$ ) and the porosity of the membrane. Our results fall within the typical range of thermal conductivity reduction already reported.

#### Power factor and zT

Fig. 10 presents the power factor (PF) of the studied membranes, illustrating the relationship between the power factor ( $S^2\sigma$ ) and the doping level for both n-type (blue) and p-type (red) silicon at a temperature of 300 K. The PF for plain membranes was determined using measured  $\sigma_P$  and  $S_P$ , while for PE membranes, it was calculated using the effective medium theory (EMT) as described by eqn (4), involving parameters  $\phi$  and  $\sigma_{PE}$  representing porosity and electrical conductivity of patterned membranes, respectively.

$$\frac{\sigma_{\rm PE}}{\sigma_{\rm P}} = \frac{1-\phi}{1+\phi} \tag{4}$$

The near-identical *S* values for both P and PE suggest that the reduction in electrical conductivity in PE membranes is solely attributed to the patterned structure rather than other factors. The highest power factor achieved was  $2.7 \times 10^{-3}$  W m<sup>-1</sup> K<sup>-2</sup>, corresponding to a specific doping level of  $7.2 \times 10^{18}$  cm<sup>-3</sup> (n-type). In addition to our data, the graph also displays information on p-type nanostructured silicon. Specifically, it includes results from studies involving nanowires,<sup>26,52</sup> holey silicon,<sup>32,53–55</sup> and ultrathin solid films. The presence of phonon drags near room temperature in membranes has provided an opportunity to

**Fig. 9** The ratio of the phononic membrane to the thermal conductivity of the plain membrane as a function of the porosity. The graph includes experimental data from previous studies, as well as data from this current work, along with results obtained from effective medium theory and Maxwell–Eucken models.

**Fig. 10** Power factor as a function of (a) doping level. The graph includes experimental data from previous studies, as well as data from this current work, encompassing both n-type silicon (indicated in blue) and p-type silicon (represented in red) at a temperature of 300 K. (b) Electrical conductivity and Seebeck coefficient (loffe plot).

Table 1 Summary of experimental values at room temperature for different silicon membrane types, including Seebeck coefficient, electrical conductivity, thermal conductivity, and zT figure of merit

| Туре         | $\kappa (W m^{-1} K^{-1})$ | $S_{ m tot} \left( \mu V \ { m K}^{-1}  ight)$ | $S_{\rm e}$ (µV K <sup>-1</sup> ) | $S_{ m ph}~(\mu V~{ m K}^{-1})$ | $\sigma ~(\mathrm{kS}~\mathrm{m}^{-1})$ | zT    |

|--------------|----------------------------|------------------------------------------------|-----------------------------------|---------------------------------|-----------------------------------------|-------|

| p-Type plain | 31                         | 424                                            | 182                               | 242                             | 10.08                                   | 0.017 |

| n-Type plain | 31                         | -451                                           | -263                              | -188                            | 13.18                                   | 0.026 |

| p-Type PE    | 18                         | 440                                            | N/A                               | N/A                             | 7.22                                    | 0.023 |

| n-Type PE    | 18                         | -504                                           | N/A                               | N/A                             | 9.45                                    | 0.04  |

enhance the Seebeck coefficient. As a result, the power factor of these membranes has increased, reaching a level comparable to that of bulk Si at similar temperatures. According to the Ioffe plot presented in Fig. 10b, TE materials exhibiting the highest PF must be positioned the right and top ends.

The reduced thermal conductivity observed in the membranes compared to bulk Si has contributed to a further increase in the zT (Fig. 1). To achieve a higher zT, it is recommended to focus on utilizing the phonon drag effect to further enhance the Seebeck coefficient while concurrently reducing the thermal conductivity. By capitalizing on these two aspects, it is possible to achieve an even larger figure of merit, thereby improving the overall thermoelectric performance of the membranes. Eventually the figure-of-merit obtained from measurements on single wafer devices range from 0.017 to 0.04. Table 1 summarizes the results measured and calculated.

## Conclusions

**Materials Advances**

Values of the thermoelectric figure-of-merit in crystalline silicon nanostructures are scarce and disperse in literature reports. The methodology of such measurement is indeed challenging. Here, we report on devices fabricated on a single silicon-on-insulator substrate dedicated to the characterization of the Seebeck coefficient, electrical conductivity and thermal conductivity of 60 nm thick silicon membranes. The Seebeck coefficients for plain p-type, phonon engineered p-type, plain n-type, and phonon engineered n-type membranes were found to be 424  $\mu V$  K  $^{-1}$ , 440  $\mu V$  K  $^{-1}$ , -451  $\mu V$  K  $^{-1}$ , and -504  $\mu V$  K  $^{-1}$ , respectively. The highest power factor achieved was 2.7  $\times$  $10^{-3}$  W m<sup>-1</sup> K<sup>-2</sup>, corresponding to a specific doping level of  $7.2 \times 10^{18} \text{ cm}^{-3}$  for n-type membranes. The thermal conductivity was measured to be 31 W  $m^{-1}$  K<sup>-1</sup> for a 60 nm thick Si membrane and 18 W m<sup>-1</sup> K<sup>-1</sup> for a porous Si membrane. We used resistive thermometry, transient thermo-reflectance and Raman thermometry to strengthen the quantitative evaluation of the Seebeck coefficient and thermal conductivity. Our findings support the possibility to increase the thermoelectric efficiency of crystalline silicon in nanonostructures. A further increase is obtained through porous patterning of the membranes. The figure-of-merit obtained from measurements on single wafer devices ranged from 0.017 to 0.04. However, we confirm that these values lie within the lower range of reported zT. Since our devices were designed with care of compatibility with conventional MEMS and CMOS processes, we suggest there is little chance that the high previously reported values can be reached in technologically plausible harvesters. Finally, we confirmed that the phonon-drag component of the Seebeck coefficient represents a non-negligible contribution even at room temperature in nanoscale systems.

## Author contributions

H. I. is the main investigator. She designed, fabricated the samples, performed Seebeck and electrical conductivity measurements, visualized and interpreted the data and conducted the modelling for thermal conductivity quantification, and wrote the manuscript. A. P. performed the Raman thermometry measurements and contributed to their interpretation. J. C. contributed to the fabrication process development. E. O. set up the electrical characterization bench and contributed to the transient thermoreflectance measurement. E. B. modelled the optical absorbance of the porous membranes. E. D. contributed to the fabrication process, sample design and the manuscript. J.-F. R. supervised the project, established the methodology and contributed to the manuscript.

## Conflicts of interest

The authors declare no potential scientific of financial conflicts of interest.

## Acknowledgements

The authors are thankful to Alex Pip and the WELCOME characterization centre for access to the transient thermoreflectance setup. H. I. was financially supported by Université de Lille. This work was supported by the French RENATECH network, the ST-IEMN Joint Research Lab, the European Research Council under the European Community's Seventh Framework Programme (FP7/2007-2013) ERC Grant Agreement no. 338179 and the French government through the National Research Agency (ANR) under project HANIBAL ANR-20-CE42-0019. This research work has been partially undertaken with the support of IEMN fabrication (CMNF) and characterization (PCMP) facilities.

```

‡ https://sites.uclouvain.be/welcome/.

```

## Notes and references

- 1 T. M. Bah, S. Didenko, D. Zhou, T. Zhu, H. Ikzibane, S. Monfray, T. Skotnicki, E. Dubois and J.-F. Robillard, *Nanotechnology*, 2022, **33**, 505403.

- 2 Z. Wang, Y. van Andel, M. Jambunathan, V. Leonov, R. Elfrink and R. J. M. Vullers, *J. Electron. Mater.*, 2011, **40**, 499–503.

- 3 J. Xie, C. Lee and H. Feng, *J. Microelectromech. Syst.*, 2010, **19**, 317–324.

- 4 A. P. Perez-Marín, A. F. Lopeandía, L. Abad, P. Ferrando-Villaba, G. Garcia, A. M. Lopez, F. X. Muñoz-Pascual and J. Rodríguez-Viejo, *Nano Energy*, 2014, **4**, 73–80.

- 5 D. Dávila, A. Tarancón, C. Calaza, M. Salleras, M. Fernández-Regúlez, A. San Paulo and L. Fonseca, *Nano Energy*, 2012, 1, 812–819.

- 6 R. Yanagisawa, N. Tsujii, T. Mori, P. Ruther, O. Paul and M. Nomura, *Appl. Phys. Express*, 2020, **13**, 095001.

- 7 R. Yanagisawa, P. Ruther, O. Paul, N. Tsujii, T. Mori and M. Nomura, *IEEE*, 2022, 114–116.

- 8 K. Ziouche, Z. Yuan, P. Lejeune, T. Lasri, D. Leclercq and Z. Bougrioua, *J. Microelectromech. Syst.*, 2017, **26**, 45–47.

- 9 M. Haras and T. Skotnicki, Nano Energy, 2018, 54, 461-476.

- 10 M. Haras, V. Lacatena, F. Morini, J.-F. Robillard, S. Monfray, T. Skotnicki and E. Dubois, *Mater. Lett.*, 2015, 157, 193–196.

- 11 D. Pinisetty and R. Devireddy, *Acta Mater.*, 2010, 58, 570–576.

- 12 M. Očko, S. Žonja and M. Ivanda, MIPRO, 2010, 16-21.

- 13 Q. Hao, G. Zhu, G. Joshi, X. Wang, A. Minnich, Z. Ren and G. Chen, *Appl. Phys. Lett.*, 2010, **97**, 063109.

- 14 J. S. Jin, J. Mech. Sci. Technol., 2014, 28, 2287-2292.

- 15 M. Haras, V. Lacatena, F. Morini, J.-F. Robillard, S. Monfray, T. Skotnicki and E. Dubois, *IEEE*, 2014, 8.5.1–8.5.4.

- P. Ferrando-Villalba, A. Lopeandia, L. Abad Muñoz, J. Llobet Sixto, M. Molina-Ruiz, G. Garcia, M. Gerbolès, F. X. Alvarez, A. Goñi, F. X. Munoz-Pascual and J. Rodríguez-Viejo, *Nanotechnology*, 2014, 25, 185402.

- 17 P. Ferrando-Villalba, A. P. Pérez-Marín, L. Abad, G. G. Dalkiranis, A. F. Lopeandia, G. Garcia and J. Rodriguez-Viejo, *Nanomaterials*, 2019, 9, 653.

- 18 Y. S. Ju, Appl. Phys. Lett., 2005, 87, 153106.

- 19 M. Asheghi, Y. K. Leung, S. S. Wong and K. E. Goodson, *Appl. Phys. Lett.*, 1997, 71, 1798-1800.

- 20 W. Liu and M. Asheghi, Appl. Phys. Lett., 2004, 84, 3819-3821.

- E. Chávez-Ángel, J. S. Reparaz, J. Gomis-Bresco, M. R. Wagner, J. Cuffe, B. Graczykowski, A. Shchepetov, H. Jiang, M. Prunnila, J. Ahopelto, F. Alzina and C. M. Sotomayor Torres, *APL Mater.*, 2014, 2, 012113.

- 22 X. Huang, S. Gluchko, R. Anufriev, S. Volz and M. Nomura, *ACS Appl. Mater. Interfaces*, 2019, **11**, 34394–34398.

- 23 J. Maire and M. Nomura, J. Appl. Phys., 2014, 53, 06JE09.

- 24 A. Boukai, Y. Bunimovich, J. Tahir-Kheli, J.-K. Yu, W. Goddard and J. Heath, *Nature*, 2008, **451**, 168–171.

- 25 D. Li, Y. Wu, P. Kim, L. Shi, P. Yang and A. Majumdar, *Appl. Phys. Lett.*, 2003, **83**, 2934.

- 26 A. Hochbaum, R. Chen, R. Diaz, W. Liang, M. Najarian,A. Majumdar and P. Yang, *Nature*, 2008, 451, 163–167.

- 27 X. Huang, S. Gluchko, R. Anufriev, S. Volz and M. Nomura, ACS Appl. Mater. Interfaces, 2019, **11**, 34394–34398.

- 28 M. Verdier, D. Lacroix, S. Didenko, J.-F. Robillard, E. Lampin, T.-M. Bah and K. Termentzidis, *Phys. Rev. B*, 2018, 97, 115435.

- 29 A. George, R. Yanagisawa, R. Anufriev, J. He, N. Yoshie, N. Tsujii, Q. Guo, T. Mori, S. Volz and M. Nomura, ACS Appl. Mater. Interfaces, 2019, 11, 12027–12031.

- 30 J. Nakagawa, Y. Kage, T. Hori, J. Shiomi and M. Nomura, *Appl. Phys. Lett.*, 2015, **107**, 023104.

- 31 M. Haras, V. Lacatena, T. M. Bah, S. Didenko, J.-F. Robillard, S. Monfray, T. Skotnicki and E. Dubois, *IEEE Electron Device Lett.*, 2016, 37, 1358–1361.

- 32 J. Tang, H.-T. Wang, D. H. Lee, M. Fardy, Z. Huo, T. Russell and P. Yang, *Nano Lett.*, 2010, **10**, 4279–4283.

- 33 R. Yanagisawa and M. Nomura, J. Phys.: Conf. Ser., 2019, 1407, 012013.

- 34 M. Nomura, J. Nakagawa, K. Sawano, J. Maire and S. Volz, *Appl. Phys. Lett.*, 2016, **109**, 173104.

- 35 B. Graczykowski, A. El Sachat, J. S. Reparaz, M. Sledzinska, M. R. Wagner, E. Chavez-Angel, Y. Wu, S. Volz, Y. Wu, F. Alzina and C. M. Sotomayor Torres, *Nat. Commun.*, 2017, 8, 415.

- 36 Q. Hao, D. Xu, H. Zhao, Y. Xiao and F. J. Medina, *Sci. Rep.*, 2018, **8**, 9056.

- 37 M. R. Wagner, B. Graczykowski, J. S. Reparaz, A. El Sachat, M. Sledzinska, F. Alzina and C. M. Sotomayor Torres, *Nano Lett.*, 2016, 16, 5661–5668.

- 38 D. Li, Y. Wu, P. Kim, L. Shi, P. Yang and A. Majumdar, *Appl. Phys. Lett.*, 2003, 83, 2934–2936.

- 39 V. Lacatena, M. Haras, J.-F. Robillard, S. Monfray, T. Skotnicki and E. Dubois, *Microelectron. Eng.*, 2014, **121**, 131.

- 40 E. Dechaumphai and R. Chen, J. Appl. Phys., 2012, 111, 073508.

- 41 R. Yanagisawa, J. Maire, A. Ramiere, R. Anufriev and M. Nomura, *Appl. Phys. Lett.*, 2017, **110**, 133108.

- 42 M. Balkanski, R. F. Wallis and E. Haro, *Phys. Rev. B:* Condens. Matter Mater. Phys., 1983, 2(8), 1928-1934.

- 43 P. J. Newby, B. Canut, J.-M. Bluet, S. Gomès, M. Isaiev, R. Burbelo, K. Termentzidis, P. Chantrenne, L. G. Fréchette and V. Lysenko, *J. Appl. Phys.*, 2013, **114**, 014903.

- 44 E. Chávez-Ángel, J. S. Reparaz, J. Gomis-Bresco, M. R. Wagner, J. Cuffe, B. Graczykowski, A. Shchepetov, H. Jiang, M. Prunnila, J. Ahopelto, F. Alzina and C. M. Sotomayor Torres, *APL Mater.*, 2014, 2, 012113.

- 45 B. Stoib, S. Filser, J. Stötzel, A. Greppmair, N. Petermann, H. Wiggers, G. Schierning, M. Stutzmann and M. S. Brandt, *Semicond. Sci. Technol.*, 2014, 29, 124005.

- 46 J. P. Hugonin and P. Lalanne, *RETICOLO software for grating analysis*, Institut d'Optique, Orsay, France, 2005, arXiv:2101: 00901, DOI: 10.48550/arXiv.2101.00901.

- 47 T. H. Geballe and G. W. Hull, Phys. Rev., 1955, 98, 940-947.

- 48 J. Sadhu, et al., Nano Lett., 2015, 15, 3159-3165.

- 49 F. Salleh, T. Oda, Y. Suzuki, Y. Kamakura and H. Ikeda, *Appl. Phys. Lett.*, 2014, **105**, 102104.

- 50 H. Ikeda and F. Salleh, Appl. Phys. Lett., 2010, 96, 012106.

Paper

- 51 A. M. Massoud, V. Lacatena, M. Haras, E. Dubois, S. Monfray, J.-M. Bluet, P.-O. Chapuis and J.-F. Robillard, *APL Mater.*, 2022, **10**, 051113.

- 52 B. M. Curtin, E. A. Codecido, S. Krämer and J. E. Bowers, *Nano Lett.*, 2013, **13**, 5503–5508.

- 53 J. Lim, et al., ACS Nano, 2016, 10, 124-132.

- 54 J. Ma, D. Gelda, K. V. Valavala and S. Sinha, *J. Appl. Phys.*, 2020, **128**, 115109.

- 55 N. Liu, T. Zhu, M. G. Rosul, J. Peters, J. E. Bowers and M. Zebarjadi, *Mater. Today Phys.*, 2020, **14**, 100224.