# **Nanoscale**

# **FEATURE ARTICLE**

View Article Online

View Journal | View Issue

Cite this: Nanoscale, 2015, 7, 8261

# Two-dimensional materials and their prospects in transistor electronics

F. Schwierz.\* J. Pezoldt and R. Granzner

During the past decade, two-dimensional materials have attracted incredible interest from the electronic device community. The first two-dimensional material studied in detail was graphene and, since 2007, it has intensively been explored as a material for electronic devices, in particular, transistors. While graphene transistors are still on the agenda, researchers have extended their work to two-dimensional materials beyond graphene and the number of two-dimensional materials under examination has literally exploded recently. Meanwhile several hundreds of different two-dimensional materials are known, a substantial part of them is considered useful for transistors, and experimental transistors with channels of different two-dimensional materials have been demonstrated. In spite of the rapid progress in the field, the prospects of two-dimensional transistors still remain vague and optimistic opinions face rather reserved assessments. The intention of the present paper is to shed more light on the merits and drawbacks of two-dimensional materials for transistor electronics and to add a few more facets to the ongoing discussion on the prospects of two-dimensional transistors. To this end, we compose a wish list of properties for a good transistor channel material and examine to what extent the two-dimensional materials fulfill the criteria of the list. The state-of-the-art two-dimensional transistors are reviewed and a balanced view of both the prospect of these devices is provided.

Received 13th February 2015, Accepted 31st March 2015 DOI: 10.1039/c5nr01052g

www.rsc.org/nanoscale

### Introduction

The FET (field-effect transistor) is the backbone of today's semiconductor electronics. It represents the basic building block of the systems of modern information and communication technology and progress in this important field critically depends on rapid improvements of FET performance. An efficient option to achieve this goal is the introduction of novel channel materials into FET technology. In this regard, 2D (two-dimensional) materials have attracted considerable attention from the transistor community. The rise of 2D materials began in 2004 with the successful preparation of graphene samples.<sup>1,2</sup> Particularly the observed high carrier mobilities raised expectations that graphene could be the perfect channel material for FETs and will become the successor of conventional semiconductors. After the enthusiastic early days of graphene transistor research it became clear, however, that graphene would not be able to fulfill these high expectations since it does not possess a bandgap which is mandatorily needed for proper FET operation.3

Just when the interest of the transistor community in graphene began to subside, 4,5 a paper on the fabrication of

that 2D transistors are of academic interest only and are useful for niche applications at best.

The strong interest of the community in 2D transistors is manifested in the remarkable number of recent review papers on this topic, each with a specific focus and flavor. Particular mention should be made of the thorough overviews on 2D materials by Butler *et al.*<sup>8</sup> and on 2D transistors by Lemme *et al.*<sup>9</sup> and of the survey on the status of TMD (transition metal dichalcogenide) as a prominent group of 2D materials beyond graphene. The reader will also appreciate the excellent discussions on 2D transistors for digital logic by Fiori *et al.*<sup>11</sup> and

single-layer MoS<sub>2</sub> FETs<sup>6</sup> gave new momentum to the research

on 2D materials. Over a surprisingly short period of time,

entire classes of new 2D materials have been discovered. A

steadily increasing number of groups worldwide are now

working intensively on 2D FETs, chipmakers pay attention to

the progress in the field, and since 2011 the ITRS (Inter-

national Technology Roadmap for Semiconductors), the stra-

tegic planning document of the semiconductor industry, has

mentioned 2D materials beyond graphene as candidates for

future electronics. Nevertheless, the prospects of the 2D

materials in electronics are controversially debated. While part

of the community is very optimistic, another fraction believes

The present paper focuses on the properties and physics of 2D materials and 2D FETs and is organized as follows. Section

for flexible electronics by Akinwande et al. 12

Institut für Mikro- und Nanoelektronik, Technische Universität Ilmenau, PF 100565, 98684 Ilmenau, Germany. E-mail: frank.schwierz@tu-ilmenau.de

2 reviews important trends in semiconductor electronics and introduces the figures of merit we later use to assess the performance of transistors. Section 3 presents an overview of the different classes of 2D materials. In section 4 we compose a wish list of properties desirable for FET channel materials and examine to what extent the 2D materials meet the requirements of our list. To keep the discussion manageable, neither the entries of the wish list nor the set of transistor figures of merit are intended to be exhaustive. Instead, we limit the discussion to a selected set of material parameters as entries for the wish list and a few key transistor figures of merit. Section 5 provides a discussion of the current status, prospects, and problems of 2D transistors, and finally section 6 concludes the paper.

# More Moore and More Than Moore – trends in semiconductor electronics

### 2.1 More Moore trends

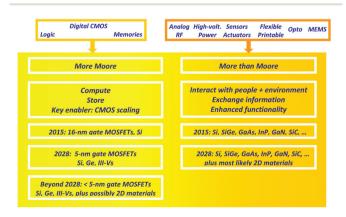

The overall semiconductor chip market has an annual volume of about \$300 billion and can, as shown in Fig. 1, broadly be divided into the two main domains More Moore and More Than Moore.

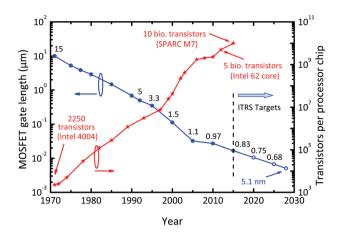

More Moore encompasses digital ICs (integrated circuits) such as microprocessors and memories and covers around 70% of the overall chip market. Interestingly, today's digital ICs are based on one single semiconducting material, Si, one single transistor type, the Si MOSFET, and one single circuit technique, Si CMOS (complementary MOS) employing both n-channel (electrons constitute the transistor's output current) and p-channel MOSFETs (holes carry the current). For decades, chipmakers have introduced CMOS ICs with an exponentially increasing number of individual MOSFETs and, simultaneously, an exponentially decreasing price per transistor, to the market. Key to this evolution is the continuous shrinking of the MOSFET size, for short scaling. As shown in Fig. 2,

Fig. 1 The More Moore and More Than Moore domains of semiconductor electronics, together with important trends and the semiconductors used in these domains. Note that the year 2028 indicates the end of the time horizon of the 2013 ITRS edition.

Fig. 2 Evolution of the MOSFET gate length and the number of transistors integrated on a single microprocessor chip. The numbers above the gate length curve indicate the processor supply voltage  $V_{\rm DD}$ . Note the continuous decrease of  $V_{\rm DD}$  in the past and the required continuation of this trend in the future. The ITRS targets refer to MOSFETs for high-performance logic as specified in the 2013 ITRS edition.<sup>7</sup>

since 2014, processors containing five billion MOSFETs with gate lengths around 20 nm have been commercially available and the introduction of a 10-billion processor has been announced for 2015.13 This trend of continuous device miniaturization and increasing circuit complexity is called Moore's Law. 14

It is important to recognize that, to follow Moore's Law, increasing circuit complexity by scaling alone is not sufficient. Instead, the electrical performance of the scaled MOSFETs must be improved as well. In particular, transistor switching speed should increase exponentially and the energy needed for a single switching event should decrease exponentially. Only if these "triple dividends of MOSFET scaling" - smaller, faster, more power-efficient - can be achieved in concert, Moore's Law will survive.

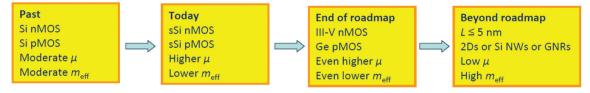

In the recent past it has become more and more difficult to achieve the required performance improvements when scaling the Si MOSFET. A material property closely related to transistor performance is the carrier mobility, and a high mobility is always beneficial for transistor speed and power efficiency. Since Si, the backbone of today's More Moore circuits, offers only moderate mobilities, rigorous efforts are made to implement alternative high-mobility MOSFET channel materials into Si CMOS. A first step was the introduction of strain into the Si MOSFET channels leading to enhanced mobilities. Meanwhile, strained Si is widely used in CMOS production16 and research on high-mobility III-V and Ge channels for future MOSFET generations is aggressively pushed forward.15,17

Beyond the horizon of the current ITRS edition, when gate lengths below 5 nm will be required, MOSFETs with highmobility (and thus light carrier effective mass) channels will encounter a fundamental problem. At this stage of scaling, the distance between the MOSFET's source and drain regions

Nanoscale Feature article

becomes so short that quantum-mechanical source-drain tunneling impedes proper FET operation. It may turn out that for sub-5 nm MOSFETs heavy effective mass materials with lower mobilities will become preferable since a heavy carrier effective mass suppresses source-drain tunneling. 18,19

#### 2.2 More Than Moore trends

More Than Moore is not primarily focused on increasing circuit complexity but rather on enhancing the functionality of ICs and electronic systems by combining digital electronics with components such as analog/RF (radio frequency) and highvoltage circuitry, sensors, actuators, etc. In the More Than Moore domain, traditionally the material basis has been much broader compared to More Moore and, apart from Si, a variety of alternative semiconductors is used to complement Si.

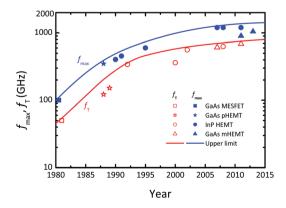

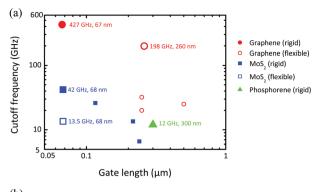

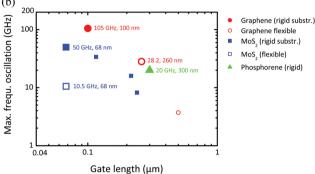

More Than Moore covers a wide and heterogeneous field, see Fig. 1. Here we focus solely on RF electronics where at present, in addition to Si, the compound semiconductors based on GaAs, InP, and GaN are very popular. It should be noted that in RF electronics only n-channel FETs are used since in most materials electrons are faster than holes. A major trend in RF electronics is the striving for higher transistor operating frequencies and for extending transistor operation into the THz range. The evolution of the frequency performance of RF FETs in terms of the characteristic frequencies  $f_{\rm T}$  (cutoff frequency) and  $f_{\rm max}$  (maximum frequency of oscillation) is shown in Fig. 3.

As can be seen, the current record  $f_{\text{max}}$  of RF FETs is slightly above 1 THz, which means that FETs capable of THz amplification with reasonable power gain are still missing. On the other hand, the frequency range around and above 1 THz is attractive for applications in a variety of fields, such as security, medicine, and ultra-high-speed communications, to name just a few.40,41 Therefore, RF device engineers are looking for alternative FET channel materials offering improved mobility and closely follow the research on 2D materials.

Fig. 3 Evolution of the cutoff frequency  $f_T$  and maximum frequency of oscillation  $f_{\text{max}}$  of RF FETs. Shown are the record  $f_{\text{T}}$  and  $f_{\text{max}}$  values reported at a certain time. MESFET: metal-semiconductor FET; HEMT: high electron mobility transistor; pHEMT: pseudomorphic HEMT; mHEMT: metamorphic HEMT. Data are taken from ref. 20-39.

### Transistor figures of merit

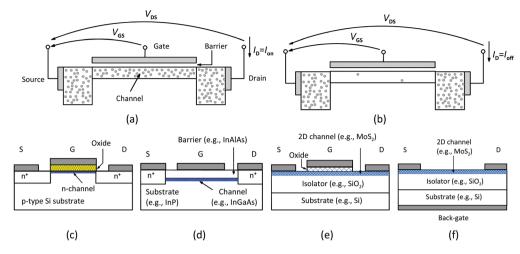

A FET consists of a channel region connecting two reservoirs of mobile charges called source and drain. The third electrode (gate) is separated from the channel by a thin barrier. The applied gate-source voltage  $V_{GS}$  controls the conductivity of the channel and the applied drain-source voltage  $V_{\rm DS}$  drives a drain current  $I_D$  through the transistor. Fig. 4 shows a generic FET, together with the structures of Si MOSFETs, III-V HEMTs, and 2D MOSFETs. FETs are devices with the ability (i) to switch and (ii) to amplify signals and provide gain. For digital electronics, i.e., More Moore, switching is relevant while amplifying signals is important for RF applications.

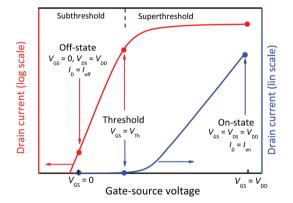

In digital logic, the FET is supposed to switch between on and off. In the on-state, see Fig. 4(a), the channel has a low resistance and a large on-current Ion can flow through it. As per definition,  $I_{on}$  is the transistor current for the bias condition  $V_{GS} = V_{DS} = V_{DD}$ . In the off-state, see Fig. 4(b), on the other hand, the FET should block the current, the channel resistance should be high, and only a very small off-current  $I_{\text{off}}$ is allowed to flow. The off-current is defined as the current flowing under the condition  $V_{GS} = 0$  and  $V_{DS} = V_{DD}$ . The gate voltage at which the transistor is just at the verge of switching on is the threshold voltage  $V_{\rm Th}$ . The transfer characteristics of a MOSFET shown in Fig. 5 indicate that in the subthreshold region  $(V_{GS} < V_{Th})$  the drain current depends exponentially on  $V_{\rm GS}$ , followed by a transition region around  $V_{\rm Th}$  and finally by the superthreshold region where the drain current is essentially linearly dependent on  $V_{GS}$ . As we have shown in Fig. 2, the supply voltage  $V_{\rm DD}$  of logic circuits has been decreased continuously over the years and a further reduction is required for the future. This means that logic transistors must switch from off to on within a very limited range of  $V_{GS}$ .

A further FOM (figure of merit) related to switching is the on-off ratio  $I_{\rm on}/I_{\rm off}$ . For FETs to be used in digital logic, on-off ratios in the range of  $\approx 10^4$ –5  $\times$  10<sup>7</sup> are required. As a basic rule,  $I_{\rm off}$  should be as low as possible and both  $I_{\rm on}$  and the onoff ratio should be as high as possible. A low  $I_{\text{off}}$  is needed for a low static power consumption of logic circuits while a high  $I_{\rm on}$  is relevant for a high transistor switching speed.

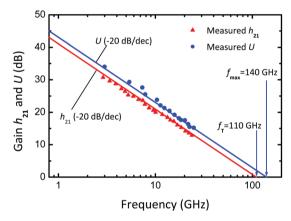

When operated as an amplifier, on the other hand, the FET does not necessarily need to switch off. Instead, in most RF amplifier configurations the FET is permanently operated in the on-state and small signals applied to its input, i.e., the gate, appear amplified at the output. The extent to which the input signal is amplified is called gain. The small-signal current gain, for example, is defined as the RF output current of the transistor divided by the RF input current. Gains are frequency dependent and decrease with increasing frequency. Two important FOMs of RF transistors are the characteristic frequencies  $f_T$  and  $f_{max}$ . The cutoff frequency  $f_T$  is the frequency at which the small-signal current gain  $h_{21}$  of the transistor has dropped to unity (i.e., 0 dB) and the maximum frequency of oscillation  $f_{\text{max}}$  is the frequency where the unilateral power gain U becomes unity. It should be noted that for most RF applications, power gain and  $f_{\text{max}}$  are more important

Fig. 4 Basic FET structures. Generic structure of a FET (a) in the on-state and (b) in the off-state. (c) Conventional Si n-channel MOSFET. (d) HEMT. (e) 2D MOSFET. (f) Back-gate 2D MOSFET frequently used for proof-of-concept purposes. Note that HEMTs and 2D MOSFETs do not possess pn junctions as present in conventional Si MOSFETs shown in (c) but rather resemble the junctionless MOSFET which is intensively investigated at present.42

Fig. 5 Transfer characteristics of an n-channel FET showing the drain current  $I_D$  as a function of the gate-source voltage  $V_{GS}$  together with the on and off operating points for CMOS logic. Note that the scale of the left current axis is logarithmic and that of the right current axis is linear.

Fig. 6 Small-signal current gain  $h_{21}$  and unilateral power gain U of a RF FET as a function of frequency, after ref. 43 and 44. The characteristic frequencies  $f_T$  and  $f_{max}$  are obtained by extrapolating the measured  $h_{21}$ and U with the characteristic slope of -20 dB per dec.

than current gain and  $f_T$ . Moreover, as a rule of thumb, the operating frequency should be lower than 20% of the used transistors'  $f_{\rm max}$  to guarantee sufficient power gain. Fig. 6 shows the small-signal current and power gains of an RF FET as a function of frequency, together with  $f_T$  and  $f_{max}$ .

Commonly the voltage gain of RF FETs is not discussed explicitly since, if both current and power gain are reported, this data pair contains information on the voltage gain. Because FETs with gapless channels, e.g. graphene MOSFETs, suffer from poor power gain, an inspection of the voltage gain is advisable, however. The frequency-dependent voltage gain A<sub>V</sub> is defined as

$$A_{\rm V} = z_{21}/z_{11} \tag{1}$$

where  $z_{21}$  and  $z_{11}$  are ac impedance parameters. At low frequencies,  $A_V$  approaches the so-called intrinsic gain  $G_{int}$ given as

$$G_{\rm int} = g_{\rm m}/g_{\rm d} \tag{2}$$

where  $g_{\rm m}$  is the transconductance (i.e., the slope of the transfer characteristics, see Fig. 5, at the dc operating point) and  $g_d$  is the drain conductance (i.e., the slope of the  $I_D$ - $V_{DS}$  output characteristics). A transistor with low intrinsic gain, e.g., caused by a large drain conductance, will always suffer from a low power gain.

All semiconductor devices generate fluctuations of voltage and current called noise. Noise is always undesirable and particularly critical for the amplification of small RF signals.

A measure for the noise generated in a transistor is the noise figure *NF*, usually given in units of dB and defined as

$$NF[dB] = 10 \times \log \frac{P_{Si}/P_{Ni}}{P_{So}/P_{No}}$$

(3)

where  $P_{\rm Si}$  and  $P_{\rm No}$  are the signal powers at the input and output, and  $P_{\rm Ni}$  and  $P_{\rm No}$  are the noise powers at the input and output, respectively. Under optimum matching and bias conditions, the noise figure reaches a minimum called minimum noise figure  $NF_{\rm min}$ . It is the relevant FOM to characterize the noise performance of RF transistors. For a good RF FET the characteristic frequencies  $f_{\rm T}$  and  $f_{\rm max}$  should be high and the minimum noise figure  $NF_{\rm min}$  should be low.

### Overview of 2D materials

Inspired by the successful preparation of graphene, researchers have intensively examined options to obtain stable 2D materials beyond graphene. These efforts include real-world experiments where 2D materials have been prepared and analyzed, as well as computational experiments where the thermodynamic stability and the band structure of existing and hypothetical 2D materials have been computed. For the latter, particularly the *Atlas of 2D Materials* reporting the properties of more than 140 different 2D materials<sup>45</sup> is worth mentioning.

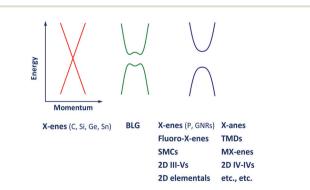

Recent experimental and theoretical efforts have shown that a variety of 2D materials beyond graphene does or should exist and that their electronic properties span the full range from metallic to insulating. Of particular interest for FET channels are the semiconducting and, to a lesser extent, the gapless semi-metallic 2D materials. Fig. 7 shows schematically the relevant parts of the band structure of different classes of these 2D materials.

### 3.1 X-enes

Nanoscale

Single-layer materials consisting of atoms of one single element arranged in a hexagonal lattice are designated as X-enes. So far, graphene as well as its Si-, Ge-, and P-based

**Fig. 7** Schematic band structure of 2D materials relevant for transistors. BLG: bilayer graphene; GNR: graphene nanoribbon; TMD: transition metal dichalcogenide; SMC: semimetal chalcogenide.

counterparts silicene, <sup>46</sup> germanene, <sup>47</sup> and phosphorene <sup>48</sup> have been experimentally realized, and the band structure of stanene, the X-ene based on tin (Sn), has been calculated. <sup>49</sup>

Compared to graphene, much less is known on the other X-enes. As of the end of 2014, the Web of Science database listed almost 91 000 entries under the search term graphene compared to 654 entries for silicene, 133 for germanene, 81 for phosphorene, and 8 for stanene. The shown in Fig. 7, graphene, silicene, germanene, and stanene are gapless and have cone-shaped conduction and valence bands. The cones are frequently called Dirac cones and, correspondingly, graphene, silicene, germanene, and stanene are designated as Dirac materials. Phosphorene, on the other hand, is a semiconductor with a sizeable gap.

#### 3.2 X-anes

The crystallographic structure of the X-anes is closely related to that of the X-enes. They also possess a hexagonal lattice of carbon (graphane), silicon (silicane), germanium (germanane), or tin (stanane) atoms. However, their lattice atoms are additionally out of plane bonded to hydrogen atoms – this is frequently called hydrogenated. Graphane was predicted to exist in 2007<sup>51</sup> and was produced experimentally shortly afterwards. Recently, germanane could also be realized experimentally. Most relevant for electronic applications is the fact that graphane, silicane, and germanane possess sizeable bandgaps.

### 3.3 Fluoro-X-enes

The structure of these materials is very similar to that of the X-anes. Here, the lattice atoms are bonded out of plane to F (fluorine) atoms. Fluorographene has already been produced experimentally and shown to have a wide gap of around, possibly even exceeding, 3 eV.<sup>54,55</sup> Theory has confirmed these results for fluorographene and predicted a gap around 1 eV for fluorosilicene while fluorogermanene seems to be gapless.<sup>45</sup>

### **3.4 TMDs**

The TMDs constitute a group of materials consisting of a transition metal M (elements of groups 4, 5, and 6 of the periodic table of elements) and a chalcogen Q, i.e., sulfur (S), selenium (Se), or tellurium (Te). These M and Q elements form covalently bonded 2D layers of the  $MQ_2$  type (e.g.,  $MoS_2$ ) with a hexagonal lattice. Single-layer TMDs consist of three atomic layers where a layer of M atoms is sandwiched between two layers of Q atoms. For example, single-layer MoS2 is composed of one layer of molybdenum atoms and two layers of sulfur atoms. Today, more than 40 different types of TMDs are known. 10 While many of them are metallic, those containing Mo and W (i.e., MoS2, WSe2, etc.) as well as several of the Hf-, Pd-, Pt-, and Zr-based TMDs are semiconductors with bandgaps of the order of 1–2 eV. 10,45 It should be noted that TMDs occur in different polytypes 1T, 1T', 2H, and 3R, where T means trigonal, T' distorted trigonal, H hexagonal, and R rhombohedral, and 1, 2, or 3 indicates the number of TMD layers in the unit cell, 56,57 which have different properties. For

example, the common 2H polytypes of the Mo- and W-based TMDs are semiconducting while their metastable counterparts of the 1T type are metallic.58

#### 3.5 **SMCs**

SMCs consist of a semimetal M (Ga or In) and a chalcogen (S or Se). In contrast to the TMDs, they are expected to occur in M<sub>2</sub>X<sub>2</sub> stoichiometry in a four-layer X-M-M-X configuration and to be semiconducting.45

### 3.6 MX-enes

There is a material class called the MAX phase family comprising more than 60 individual ternary layered materials.<sup>59</sup> These materials have a hexagonal lattice and the composition  $M_{n+1}AX_n$  where M is an early transition metal, A is a group 13 or 14 element, X is either carbon or nitrogen, and n is an integer equal to 1, 2, or 3. The bonds between the M and X atoms are much stronger than the M-A bonds so that the A atoms can easily be removed, e.g., by an acid treatment. By a subsequent sonication, single  $M_{n+1}X_n$  layers, the so-called MXenes, can be obtained. As the first MX-ene, Ti<sub>3</sub>C<sub>2</sub> has been successfully prepared from the MAX material Ti<sub>3</sub>AlC<sub>2</sub>, 60 soon followed by the experimental verification of five further MXenes,61 and the existence of even more MX-enes has been predicted. Furthermore, F2, (OH)2, and O2 groups can be attached to the pure MX-enes of the M2X configuration, resulting in the formation of the modified MX-enes M2XF2, M2X(OH)2, and MXO<sub>2</sub>. 62 Several modified MX-enes have been predicted to be semiconductors with sizeable bandgaps.<sup>62</sup>

### 3.7 Further 2D materials

By first-principles calculations, the phonon properties and band structures of entire classes of 2D IV-IV and III-V compounds and of many other 2D materials have been investigated. It has been shown that a large body of these 2D materials with both hexagonal and tetragonal lattice structures should be stable and show bandgaps between 0.2 and 5 eV. 45,63,64 Although it is uncertain whether all these 2D materials can be synthesized, at least part of them may become available for experiments in the future.

### 3.8 Production of 2D materials

To fabricate 2D transistors, first the 2D starting material must be produced, preferably in the form of large-area sheets with uniform thickness and high crystallographic quality. Layered van der Waals materials, where the stacked layers are bound by weak van der Waals forces, can be exfoliated. Mechanical exfoliation is widely used to produce graphene, 1 TMDs, 6 and phosphorene<sup>48</sup> layers. While this approach is simple and does not require expensive equipment, it is time consuming and provides flakes of limited size only. Liquid exfoliation as a second exfoliation method delivers 2D flakes dispersed in a liquid. 65 This method is very effective, but the dispersed flakes are small, which makes transistor and circuit processing challenging.

As an alternative, wafer-scale 2D materials can be grown on substrates. Epitaxial graphene on SiC has successfully been formed and used for transistor processing.66 Graphene can also be grown by CVD (chemical vapor deposition) on metals and subsequently be transferred to insulating substrates such as oxidized Si wafers.<sup>67</sup> Furthermore, different TMDs such as MoS<sub>2</sub>, WS<sub>2</sub>, and WSe<sub>2</sub> have been grown by CVD directly on oxidized Si wafers. 68,69 Finally, silicene has been grown on metals and transferred to SiO<sub>2</sub>/Si substrates for device processing.<sup>70</sup>

# Properties of 2D materials relevant for transistors

### 4.1 The ideal material for a FET channel - a wish list†

To assess the potential of novel materials for FET channels it is not sufficient to consider only one single material property such as the carrier mobility. Instead, a set of properties should be examined to get a realistic impression on the suitability of the new material for transistors. Therefore, in the following we compose a (certainly not complete) wish list for the material properties of a FET channel, particularly for use in digital logic and RF FETs, and examine the extent to which the 2D materials meet our wishes. In the discussion it should always be kept in mind that research on most of the 2D materials has just begun and is in an embryonic stage compared to the conventional 3D bulk semiconductors such as Si, Ge, and the III-V compounds. This leads to the situation that, while our wish list itself is well established and relies on the experiences of decades of transistor research, the available data for the relevant properties of the 2D materials are rather fragmentary.

**4.1.1** Wish list entry #1: bandgap. The bandgap is a key property of semiconductors. It decisively affects their applicability to electronic devices and the existence of a gap is essential for proper FET operation. As discussed in section 2.3, FETs for digital logic need a high on-off ratio. While the on-current of a FET is not directly related to the bandgap  $E_G$ , the offcurrent strongly depends on EG according to

$$I_{\rm off} \propto \exp \frac{-E_{\rm G}}{mk_{\rm B}T}$$

(4)

where m is a factor of 2 (ref. 72) or larger (depending on the specific FET design),  $k_{\rm B}$  is the Boltzmann constant, and T is the temperature. Thus, the on-off ratio follows

$$\frac{I_{\rm on}}{I_{\rm off}} \propto \exp \frac{E_{\rm G}}{mk_{\rm B}T}$$

(5)

Estimations suggest that at room temperature a gap of the order of 400 meV is needed to achieve a sufficiently good switch-off and the required on-off ratios. 72-74

Since RF FETs can permanently be operated in the on-state and do not need to switch off, one might conclude that here a gap is not needed. Unfortunately, the situation is more

<sup>†</sup>The idea for the title of this section originates from ref. 71.

Nanoscale Feature article

complex. It has been discussed in detail that to achieve a high power gain and high  $f_{\rm max}$ , the FET needs to show a sufficiently good saturation of the drain current and for that, in turn, a gap is needed.<sup>3</sup> Current gain and  $f_T$ , on the other hand, are less affected by a missing or weak current saturation. Thus, transistors with gapless channels can provide high current gain and  $f_T$  but suffer from poor power gain and  $f_{max}$ . It is not exactly known how wide the gap of the channel of a good RF FET should be. Most likely, the requirements are less stringent than for logic FETs. The fastest and least noisy RF FETs are InP HEMTs<sup>32</sup> and GaAs mHEMTs<sup>75,76</sup> having In<sub>x</sub>Ga<sub>1-x</sub>As channels with high In contents x ranging from 0.7 ( $E_G \approx 0.65$  eV) to 1 (i.e., InAs,  $E_G = 0.35$  eV). Experiments with InSb channel HEMTs ( $E_G$  InSb = 0.17 eV), on the other hand, revealed that these transistors, despite being fast, show lower  $f_T$  and  $f_{max}$  compared to InP HEMTs and GaAs mHEMTs with a similar gate length.77,78 This suggests that the 0.17 eV gap of InSb might already be too narrow for ultra-high-performance RF FETs.

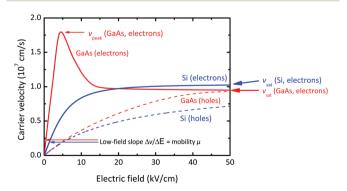

4.1.2 Entry #2: carrier transport and effective mass. Logic and RF FETs should be fast, i.e., they should react quickly on variations of their input signals, and show a large on-state current. For this, fast carriers are needed. Measures for the speed of carrier transport are the mobility  $\mu$ , the peak velocity  $v_{\rm peak}$ , and the saturation velocity  $v_{\rm sat}$ . When a low electric field **E** acts on a carrier, its drift velocity  $\nu$  is given by  $\nu = \mu \times \mathbf{E}$ . The mobility is inversely proportional to the carrier effective mass  $m_{\rm eff}$  and a light  $m_{\rm eff}$  is a precondition for a high  $\mu$ . Under highfield conditions, the carrier velocity no longer follows the field linearly. The high-field velocity for holes shows a soft saturation and approaches  $v_{sat}$  at high fields. For electrons, the situation is more diverse. In some semiconductors (e.g., GaAs), the electron velocity shows a pronounced peak ( $\nu_{peak}$ ) at a certain field, then decreases at higher fields, and eventually approaches the saturation velocity. In other semiconductors, e.g., Si, soft saturation without a velocity peak occurs. Fig. 8 shows exemplarily the  $\nu$ -E (velocity-electric field) characteristics for electrons and holes in Si and GaAs. The channel material of a fast FET should show a high mobility (and thus a light  $m_{\rm eff}$ ), preferably combined with a high  $v_{\rm peak}$  and/or  $v_{\rm sat}$ .

Fig. 8 Velocity-field characteristics for electrons and holes in Si and GaAs. Note the peak of the electron velocity in GaAs and the soft saturation of the other v-E characteristics.

For logic FETs, a high mobility and a high saturation velocity are always desirable. It should be mentioned, however, that Si MOSFETs show surprisingly good switching characteristics in spite of the rather moderate  $\mu$  (200–500 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) and  $\nu_{\rm sat}$  (10<sup>7</sup> cm s<sup>-1</sup>). The  $\ln_x Ga_{1-x}As$  channels of the best RF FETs, *i.e.*,  $\ln$ P HEMTs and GaAs mHEMTs, show mobilities of 10 000–15 000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and peak velocities of 3–4 × 10<sup>7</sup> cm s<sup>-1</sup>, and alternative channel materials that are to compete with  $\ln_x Ga_{1-x}As$  for high-performance RF FETs should show at least similar transport characteristics, combined with an appropriate bandgap. Reasonably good RF performance, however, can be achieved already with lower mobility channels, *e.g.*, Si channels of RF Si MOSFETs, provided the contact resistance (see entry #4) is low and the scale length (entry #5) is short.

**4.1.3 Entry #3: heat transport.** If a voltage is applied to a FET and a current is flowing through its channel, electrical energy is converted into heat and this heat must be removed to avoid unacceptable self-heating. To accomplish an effective heat removal, the channel material should show a high thermal conductivity  $\kappa$ .

The thermal conductivity of the channel material, however, does not tell the whole story of heat transport, in particular if the transistor is located on a substrate different from the channel material. 2D FETs, such as graphene or TMD FETs (see Fig. 4e showing a MoS<sub>2</sub> MOSFET), are frequently realized on the surface of oxidized Si wafers. Here, the heat generated in the channel first has to cross the channel–SiO<sub>2</sub> interface acting as a thermal boundary resistance  $R_{\rm TB}$ , move through the SiO<sub>2</sub> layer, and then cross the SiO<sub>2</sub>–substrate interface forming a second  $R_{\rm TB}$  before it can spread across the Si substrate.<sup>79</sup> To limit self-heating, the thermal conductivity of the FET channel material and of all materials underneath should be high and the thermal boundary resistances of all interfaces between the channel and the back side of the chip should be low.

4.1.4 Entry #4: contact resistance. In a FET, the gatesource voltage controls the channel conductivity and thus the drain current  $I_D$ . A closer inspection shows that not the gatesource voltage applied between the gate and source terminals, but rather the intrinsic gate-source voltage  $V_{GS-int}$ , i.e., the potential difference between the gate and the source-sided end of the channel, is controlling the current. Carriers coming from the source terminal first cross the metal-semiconductor interface which hinders the carrier flow and acts as a resistance called source contact resistance  $R_{\text{co-S}}$ . Next, the carriers flow through an ungated semiconductor region until they reach the channel underneath the gate. This ungated region represents the source series resistance  $R_{\text{ser-S}}$ . The overall parasitic resistance at the source side,  $R_{\text{S}}$ , is the sum  $R_{\text{co-S}} + R_{\text{ser-S}}$ . The same situation occurs at the drain side of the FET leading to the parasitic drain resistance  $R_{\rm D}$ .

Due to the voltage drop across  $R_S$ , part of the applied  $V_{GS}$  is lost for the control of the current as can be seen from

$$V_{\rm GS} = V_{\rm GS-int} + I_{\rm D}(R_{\rm co-S} + R_{\rm ser-S}) = V_{\rm GS-int} + I_{\rm D}R_{\rm S}$$

(6)

Similarly, the applied drain-source voltage  $V_{DS}$  is different from the intrinsic drain-source voltage  $V_{DS-int}$  according to

$$V_{\rm DS} = V_{\rm DS-int} + I_{\rm D}(R_{\rm S} + R_{\rm D}) \tag{7}$$

The parasitic source and drain resistances  $R_S$  and  $R_D$ , and thus the contact resistance  $R_{co}$ , deteriorate transistor performance. Therefore, the  $R_{co}$  should be as low as possible.

The contact resistance is proportional to the inverse of the contact width, i.e.,  $R_{\rm co} \propto 1/W$ . To compare the contact resistances obtained from structures with different contact widths,  $R_{co}$  is commonly normalized with respect to the contact width and is given in units of  $\Omega$  mm.

4.1.5 Entry #5: scale length and channel thickness. The scale length  $\lambda$  is not a material property in the strict sense. It provides, however, valuable information on the electrostatic integrity, the ability to suppress undesirable short-channel effects, and the scaling limits of a certain FET design. In ref. 80, the scale length expression

$$\lambda = \sqrt{t_{\rm ch} t_{\rm bar} \varepsilon_{\rm ch} / \varepsilon_{\rm bar}} \tag{8}$$

has been derived, where  $\varepsilon_{\rm ch}$  and  $\varepsilon_{\rm bar}$  are the dielectric constants of the channel and the barrier separating gate and channel (e.g., the gate oxide in MOSFETs),  $t_{ch}$  is the thickness of the channel region, and  $t_{\rm bar}$  is the barrier thickness. If a transistor with a gate length L fulfills the condition

$$L \geq a \times \lambda$$

(9)

where a is a constant, short-channel effects, most notably the undesirable degradation of the subthreshold behavior and the increase of the off-current, are sufficiently suppressed. Therefore, a short scale length and thus a combination of a thin channel region and a thin barrier are always desirable.

Three issues related to the scale length should be borne in mind. First, eqn (8) has been derived for fully depleted SOI (silicon on insulator) MOSFETs with relatively thick Si channels. Thus, strictly speaking, eqn (8) does not apply to FETs with extremely thin channels, e.g. channels of 2D materials. Second, the effect of the insulating layer underneath the channel has not been taken into account. Third, the scale length concept is valid only for semiconducting channels and does not apply to gapless channels. The main message of eqn (8) and (9) is that a thin channel region is beneficial for suppressing short-channel effects and FET scaling. If not only the trend is of interest, but actual numbers for the scale length of MOSFETs with 2D channels are needed, more elaborate scale length expression developed for atomically thin channels should be used.81,82

4.1.6 Addendum to entry #2. We have seen that FET channel materials having high mobility and light effective mass are desirable, and indeed, chipmakers put significant effort in increasing the channel mobility in CMOS logic FETs. It should be noted, however, that a light effective mass may also cause two problems. First, a material with a light effective mass  $m_{\rm eff}$  has a low DOS (density of states), and a low DOS means that, to achieve a certain variation of the channel charge  $\Delta Q_{\rm ch}$  (and thus of the drain current), a larger variation of the gatesource voltage  $\Delta V_{\rm GS}$  is needed.<sup>83</sup> The consequence of this effect called the DOS bottleneck is that FETs with light-meff channels may suffer from a depressed control effect of the gate and thus a degraded transconductance  $g_{\rm m}$  that obeys the relation

$$g_{\rm m} \propto \nu_{\rm eff} \frac{\Delta Q_{\rm ch}}{\Delta V_{\rm GS}}$$

(10)

where  $v_{\rm eff}$  is the effective carrier velocity in the channel, which is related to  $\mu$ ,  $\nu_{\text{peak}}$ , and  $\nu_{\text{sat}}$ . While a light  $m_{\text{eff}}$  is beneficial for a high  $v_{\rm eff}$ , the opposite is the case for  $\Delta Q_{\rm ch}/\Delta V_{\rm GS}$ . Thus, a light  $m_{\rm eff}$  is preferable only as long as its positive effect on  $v_{\rm eff}$ overcompensates its deteriorating influence on  $\Delta Q_{\rm ch}/\Delta V_{\rm GS}$ .

Second, beyond the horizon of the 2013 ITRS edition, when gate lengths of 5 nm and below will be needed and source-todrain tunneling will become an issue, FETs with high-mobility light-meff channels may fail and channel materials with wider bandgap, heavier carrier effective mass (and, consequently, lower mobility) may be preferred to suppress source-to-drain tunneling. 18,19

Table 1 summarizes our discussion on the wish list for the properties of FET channel materials.

Good carrier transport properties, most notably a high mobility, are important for a high on-current and a high  $f_T$ , while bandgap and scale length are most relevant for the off-current and, to a certain extent, for drain current saturation and  $f_{\text{max}}$ .

### 4.2 Bandgap of 2D materials

The bandgap information for 2D materials available in the literature comprises a limited amount of measured data and a

Table 1 Wish list for the properties of an ideal FET channel material. hp: high-performance; L: gate length. Note that for logic (L > 5 nm) a carrier effective mass < 0.1 is desirable in general while for holes  $m_{\rm eff} \le$ 0.2 is probably more realistic since for many semiconductors the effective mass for holes is noticeably heavier than for holes. The effective mass is given in units of the electron rest mass  $m_0$

| Entry<br># | Property                           | Desirable                                                                       |

|------------|------------------------------------|---------------------------------------------------------------------------------|

| 1          | Bandgap                            | Logic: ≥0.4 eV                                                                  |

|            | 0.1                                | hp RF: sizeable, probably lower limit<br>below 0.4 eV and optimum above 0.17 eV |

| 2          | Carrier transport                  | below off ev and optimum above off, ev                                          |

|            | Carrier effective                  | Logic: light ( $L > 5$ nm), $m_{\text{eff}} < 0.1$                              |

|            | mass                               | heavy $(L \le 5 \text{ nm}), m_{\text{eff}} \ge 0.5$                            |

|            |                                    | hp RF: very light, $m_{\rm eff} < 0.05$                                         |

|            | Mobility                           | hp Logic: high, $> 500 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$              |

|            | ·                                  | hp RF: very high, > 10 000 cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup>      |

|            | Peak/saturation                    | Logic: high, >10 <sup>7</sup> cm s <sup>-1</sup>                                |

|            | velocity                           | hp RF: very high, $\geq 3 \times 10^7$ cm s <sup>-1</sup>                       |

| 3          | Heat transport                     |                                                                                 |

|            | Thermal                            | High                                                                            |

|            | conductivity                       |                                                                                 |

|            | Thermal boundary                   | Low                                                                             |

|            | resistance                         |                                                                                 |

| 4          | Contact resistance                 | Low, $\leq 0.03 \Omega \text{ mm}$                                              |

| 5          | Scale length,<br>channel thickness | Small                                                                           |

Nanoscale

wide body of results obtained from first-principle (*ab initio*) calculations. Calculations provide not only the bandgap itself, but the entire band structure, from which the carrier effective masses can be extracted. Thus, first-principle calculations are a very useful means of assessing the suitability of a semiconductor for FET channels. It should be mentioned, however, that different methods of first-principle calculations can lead to quite different bandgaps for one and the same material. The popular DFT (density functional theory) systematically underestimates the bandgap, while computationally more

demanding approaches, such as GW, predict wider gaps

which, however, in some cases exceed the measured gaps. 45,84

Two examples for the considerable differences between the bandgaps obtained from DFT calculations and those calculated using more rigorous methods are given below. For germanane, the bandgap predicted by DFT ranges from 0.95 eV<sup>85</sup> to 1.53 eV<sup>53</sup> compared to values in the range of 1.84 eV<sup>45</sup> to 3.6 eV86 obtained by other methods and a measured gap of 1.59 eV.<sup>53</sup> As a second example we consider GNRs. For N =7 armchair GNRs (N is the number of carbon atoms along the GNR width and N = 7 corresponds to a width of about 0.74 nm), a gap of 3.8 eV has been calculated by the GW method87 compared to 1.5-1.6 eV obtained by DFT87,88 and measured gaps of 2.3-2.8 eV. 89,90 Thus, calculated bandgaps should be treated as estimates rather than accurate predictions, and those obtained by DFT calculations as a lower limit. On the other hand, the shape of the individual bands calculated by DFT and the extracted carrier effective masses can be considered as reasonable guides.<sup>45</sup>

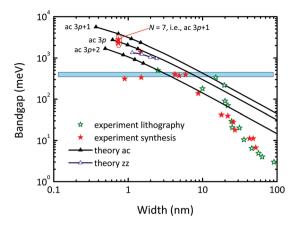

Large-area graphene is gapless and the same holds for silicene and germanene. There are, however, options to open a gap in these materials. For graphene, the first approach is to form narrow GNRs by either chemical synthesis 191,92 or lithographic patterning. Chemically synthesized GNRs with atomically precise edges have been reported while patterned GNRs typically show non-ideal edges that degrade carrier transport. Fig. 9 compiles theoretical bandgap data (calculated by the GW method) together with experimental bandgap data for GNRs and shows the general trend of an increasing gap for decreasing width. As can be seen, narrow ribbons having a width of 10 nm or less are needed to achieve the 0.4 eV gap required for digital logic.

The second option to open a gap in graphene is by applying a perpendicular electric field to BLG, *i.e.*, two graphene layers, one located directly on top of the other. As shown in Fig. 7, the conduction and valence bands of biased BLG are not parabolic as for most other semiconductors, but Mexicanhat-shaped. For FET-relevant BLG structures, realistically gaps up to 130 meV can be expected. This might be helpful for RF FETs but is not sufficient for digital logic FETs.

Recent calculations have predicted a gap opening in silicene and germanene nanoribbons<sup>98</sup> as well as in single-layer silicene and germanene when a vertical electric field is applied.<sup>99</sup> For a given field, however, the gap in silicene and germanene is smaller than that in biased BLG. Thus, regarding the bandgap, large-area silicene and germanene are not

**Fig. 9** Bandgap of GNRs vs. ribbon width. Shown are theoretical data obtained by the GW method for ac (armchair) GNRs of the 3p, 3p+1, and 3p+2 families (full triangles and lines, p is an integer) and for zz (zigzag) GNRs from ref. 87, together with measured results for chemically synthesized<sup>89,90,95</sup> and lithographically patterned<sup>93,94</sup> GNRs.

suited for logic FETs and their potential for RF FETs is unclear.

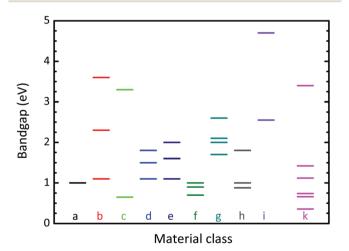

The bandgaps of the 2D materials (except Dirac materials, nanoribbons, BLG, and biased silicene and germanene) are summarized in Fig. 10. To guarantee consistency, all gaps shown are calculated by DFT. True semiconductors ( $E_{\rm G}$  = 0.5–2 eV) are phosphorene, germanane, fluorosilicene, the Mo- and

Fig. 10 Bandgap of semiconducting and insulating 2D materials calculated by DFT (data taken from ref. 45 unless otherwise stated). The letters indicate the material class. (a) Semiconducting X-enes (phosphorene, 100 note that graphene, silicene, and germanene are gapless). (b) X-anes (from top to bottom graphane, silicane, germanane). (c) Fluoro-X-enes (fluorographene, fluorosilicene, note that fluorogermanene is gapless). (d) Mo-based TMDs (MoS<sub>2</sub>, MoSe<sub>2</sub>, MoTe<sub>2</sub>). (e) W-based TMDs (WS<sub>2</sub>, WSe<sub>2</sub>, WTe<sub>2</sub>). (f) Further disulfides (HfS<sub>2</sub>, ZrS<sub>2</sub>, TiS<sub>2</sub>). (g) SMCs (GaS, InS, GaSe, InSe). (h) MX-enes<sup>62,101</sup> (top: Sc<sub>2</sub>CO<sub>2</sub>, middle: Hf<sub>2</sub>CO<sub>2</sub>, Sc<sub>2</sub>CF<sub>2</sub>, Ti<sub>2</sub>CO<sub>2</sub> (all 1 eV), bottom: Zr<sub>2</sub>CO<sub>2</sub>). (i) BN, SiC. Also shown are the gaps of conventional 3D semiconductors labeled as material class k (GaN, GaAs, Si, In<sub>0.53</sub>Ga<sub>0.47</sub>As, Ge, InAs).

W-based TMDs, as well as HfS2, ZrS2, and TiS2, GaSe, InSe, and several MX-enes. Graphane, silicane, fluorographene, GaS, InS, and SiC can be considered as wide bandgap semiconductors while BN is an insulator. For comparison, bandgap data for conventional 3D semiconductors widely used for FET channels are also shown in Fig. 10.

Due to its wide gap, BN is not really a candidate channel material. It has, however, successfully been used as a gate dielectric for graphene MOSFETs<sup>102</sup> and moreover shown to have a beneficial effect on the mobility in graphene channels underneath or above it. 102,103

The bandgap of TMDs and phosphorene depends on the layer number. It is widest for single layers and gradually decreases with increasing layer number toward the bulk value. This is important since the channels of experimental TMD and phosphorene MOSFETs frequently consist of few-layer material instead of single layers. The thickness dependence of the gap is particularly pronounced for phosphorene where the gap decreases from 1 eV for single layers (see Fig. 10) down to 0.67 and 0.52 eV for bilayer and trilayer materials. 100

In summary we state that in terms of bandgap many 2D materials fulfill the requirements of our wish list and therefore are suitable for FET channels.

### Carrier transport and effective mass

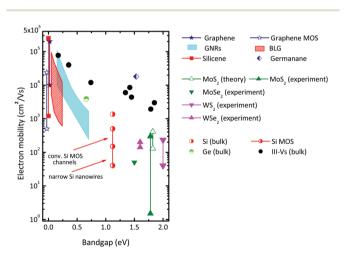

It is well established that the carrier mobility of semiconductors tends to decrease with increasing bandgap. From Fig. 11 showing this trend for the electron mobility  $\mu_n$ , we see that for the III-V compounds (black full circles), the electron mobility

Fig. 11 Room-temperature electron mobility vs. bandgap for different materials. The data for the conventional 3D bulk semiconductors taken from the compilation in ref. 44 relate to undoped material. III-V materials (black solid circles), from left to right InSb, InAs, In<sub>0.53</sub>Ga<sub>0.47</sub>As, InP, GaAs, In<sub>0.52</sub>Al<sub>0.48</sub>As, Al<sub>0.3</sub>Ga<sub>0.7</sub>As, Ga<sub>0.51</sub>In<sub>0.49</sub>P. Experimental data for graphene and simulated mobilities for GNRs and BLG taken from the compilation in ref. 3. Calculated mobilities for silicene and germanene taken from ref. 104-106. Simulated MoS<sub>2</sub> mobilities taken from ref. 104, 107 and 108, experimental MoS<sub>2</sub> data taken exemplarily from ref. 6 and 109-112, and those for WS<sub>2</sub>, MoSe<sub>2</sub> and WSe<sub>2</sub> from ref. 113, 114, 124 and

reduces from 77 000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for the narrow-bandgap InSb to 3000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for the wider-bandgap  $Ga_{0.51}In_{0.49}P$  ( $E_G =$ 1.85 eV). Si  $(E_G = 1.12 \text{ eV})$  and Ge  $(E_G = 0.66 \text{ eV})$  follow this tendency although for these materials the electron mobility is lower than that of the III-V compounds with a comparable gap. Also graphene cannot escape from this mobility-bandgap trend. Suspended gapless graphene shows very high electron mobilities of up to 200 000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The electron mobility in gapless graphene on insulating substrates is lower, but still impressively high as shown in Table 2. The gap opening in GNRs and biased BLG results, however, in a dramatic mobility reduction.

The electron mobility data reported by early 2015 for 2D materials beyond graphene are also included in Fig. 11. For MoS<sub>2</sub>, phonon limited mobilities, i.e., the upper mobility limit for defect-free undoped material, ranging from 130 cm<sup>2</sup> V<sup>-1</sup>  $s^{-1}$  (ref. 104) to 410 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (ref. 107), have been calculated and mobilities between 1 and 300 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> have been extracted from experimental MoS2 MOSFET structures, see, e.g., ref. 6, 109-112. Note that (i) the mobility reported for back-gated MoS<sub>2</sub> MOSFETs (a few to a few tens of cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) is lower than the mobility observed in top-gated MoS2 FETs (several tens to a few hundreds of cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), and (ii) for topgated MoS2 FETs occasionally electron mobilities of up to  $1000 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  (ref. 121) have been reported. These data are not included in Fig. 11 since it most likely results from an irregular extraction approach. 122,123

For single-layer WSe<sub>2</sub>, a hole mobility of 250 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> has been reported126 that compares favorably with the best electron mobilities around 200 cm2 V-1 s-1 observed in multilayer WSe<sub>2</sub> <sup>114</sup> and in ref. 127 it has been shown that the hole mobility in WSe2 can indeed be higher than the electron mobility. In few-layer phosphorene, a remarkable hole mobility of 1000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> has been measured. 128

Velocity-field characteristics for gapless graphene have been simulated and measured, and for BLG, GNRs, silicene, and MoS<sub>2</sub> high-field transport data have been simulated. The reported  $\nu$ -E characteristics of 2D materials show a soft saturation with a slight decline of the velocity at high fields. Table 3 summarizes the available saturation and peak velocity data for 2D materials. These high-field transport data can be compared with the  $\nu$ -E characteristics for Si and GaAs in Fig. 8.

It should be mentioned that for future generations of Sibased logic ICs, ultra-thin-body SOI MOSFETs and possibly Si nanowire MOSFETs with ultra-small body cross-section will be

Table 2 Measured electron mobility in gapless graphene produced by different methods. Note that the predicted upper limit for the mobility in gapless graphene on SiO<sub>2</sub>/Si is 40 000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (ref. 120)

| Graphene<br>type | Supporting layer/<br>substrate        | Mobility<br>(cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | Ref. |

|------------------|---------------------------------------|----------------------------------------------------------------|------|

| Exfoliated       | SiO <sub>2</sub> /Si                  | 24 000                                                         | 115  |

| Exfoliated       | WS <sub>2</sub> /SiO <sub>2</sub> /Si | 38 000                                                         | 116  |

| CVD              | SiO <sub>2</sub> /Si                  | 16 000                                                         | 117  |

| Epitaxial        | Si-face SiC                           | 2000                                                           | 118  |

| Epitaxial        | C-face SiC                            | 8700                                                           | 119  |

Nanoscale Feature article

Table 3 Peak and saturation velocities for 2D materials and the corresponding fields (in kV cm<sup>-1</sup>) and carrier sheet densities

| Material         | $v_{\rm peak} \left(10^7 \ {\rm cm \ s^{-1}}\right)$ | $v_{\rm sat}  (10^7  {\rm cm \ s^{-1}})$ | Comment                                                        | Ref. |

|------------------|------------------------------------------------------|------------------------------------------|----------------------------------------------------------------|------|

| Graphene         | _                                                    | 1-3 (a) 20                               | Exp. + fit, different $n_S$                                    | 129  |

| Graphene         | 5.8 <b>(a)</b> 15                                    | 5.2 @ 50                                 | Sim., $n_S = 10^{11} \text{ cm}^{-2}$                          | 130  |

| BLG              | 3.4 (a) 5                                            | 2.9 (a) 20                               | Sim., $n_S = 5 \times 10^{11} \text{ cm}^{-2}$                 | 131  |

| BLG              | _                                                    | 3.0 @ 25                                 | Sim., $n_S = 10^{12} \text{ cm}^{-2}$ , $E_G = 0.1 \text{ eV}$ | 130  |

| GNR              | 3.7 (a) 10                                           | <3 (a) >30                               | Sim., $n_S = 10^{12} \text{ cm}^{-2}$ , $w = 10.1 \text{ nm}$  | 132  |

|                  | >3.1 (a) >100                                        | _                                        | Sim., $n_S = 10^{12} \text{ cm}^{-2}$ , $w = 2.62 \text{ nm}$  |      |

| GNR              | _                                                    | 3.3 @ 25                                 | Sim., $n_S = 10^{12} \text{ cm}^{-2}$ , $E_G = 0.4 \text{ eV}$ | 130  |

| Silicene         | 0.5 (a) 30                                           | 0.46 (a) 50                              | Sim.                                                           | 104  |

|                  | &                                                    | 0.39 @ 100                               |                                                                |      |

| $MoS_2$          | _                                                    | 0.34 @ 100                               | Sim.                                                           | 104  |

| MoS <sub>2</sub> | _                                                    | 1.5 @ 100                                | Sim.                                                           | 108  |

| 2                |                                                      |                                          |                                                                |      |

needed and that in these structures, the mobility is degraded and much smaller compared to bulk Si. For example, in sub-5 nm diameter Si nanowire MOS structures, the electron mobility at low perpendicular effective fields can be below 100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and drop further at higher effective fields down to a few tens of cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. 133,134 Thus, several 2D semiconductors can be considered as a viable alternative.

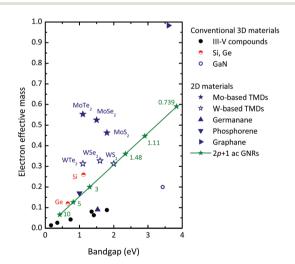

If carrier transport data for a new material are not available, an examination of the material's band structure and carrier effective mass can be helpful. Although the effective mass is not the only quantity influencing the mobility, a light effective mass is always an indication for a high mobility. In Fig. 12 the electron effective mass of 2D materials and of conventional semiconductors is plotted as a function of the bandgap.

For conventional semiconductors (Si, Ge, III-V compounds) the hole mobility  $\mu_{\rm p}$  is always lower than the electron mobility. This is particularly true for the III-V compounds with very high electron mobility. The ratio  $\mu_p/\mu_n$  is around 0.5 for Ge, 0.3

Fig. 12 Electron effective mass of 2D and conventional 3D semiconductors vs. bandgap. III-V compounds (black solid circles), from left to right InSb, InAs, In<sub>0.53</sub>Ga<sub>0.47</sub>As, InP, GaAs, Al<sub>0.3</sub>Ga<sub>0.7</sub>As. Data for TMDs and graphane from ref. 45, for germanane from ref. 53, for GNRs from ref. 135, and for phosphorene from ref. 136 and 137. The numbers at the GNR data points indicate the ribbon width according to the width-gap relationship from ref. 87.

for Si, 0.05 for GaAs, and approaches 0.01 for the narrow bandgap compounds InAs and InSb. For the Mo- and W-based TMDs<sup>45</sup> and for germanane,<sup>53</sup> as well as for phosphorene for transport in the armchair direction,  $m_{\text{eff-n}}/m_{\text{eff-p}}$  ratios  $(m_{\text{eff-n}} \text{ and } m_{\text{eff-p}} \text{ are the electron and hole effective masses})$  of 0.8-1 have been calculated and band structure calculations for BLG and GNRs also reveal a high degree of symmetry of the top of the valence band and the bottom of the conduction band. This suggests  $\mu_p/\mu_n$  ratios close to unity for these materials. For CMOS logic,  $\mu_{\rm n} \approx \mu_{\rm p}$  is highly desirable since under these conditions a symmetric design of n- and p-channel MOSFETs is possible.

When comparing the electron mobilities of the 2D materials in Fig. 11 with those of the conventional 3D semiconductors it seems that the semiconducting 2D materials show rather moderate mobilities and, with the exception of germanene, do not compete well. This leads us to the conclusion that the 2D materials cannot compete with the highmobility III-V compounds and will not be suitable for ultrafast high-performance transistors. On the other hand, their mobilities are appropriate for many other applications where high speed is not of primary importance. The calculated electron mobility of more than 18 000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for germanane, 106 on the other hand, is very promising. However, this result needs to be confirmed by experiments and to be reproduced by calculations of other groups.

### 4.4 Heat transport

Table 4 summarizes the currently available data for the thermal conductivity of 2D materials in comparison with that of 3D bulk materials. The thermal conductivity of suspended graphene exceeds that of metals (e.g.,  $\kappa_{Cu} = 400 \text{ W m}^{-1} \text{ K}^{-1}$ ) and the maximum reported record value from ref. 138 is even above that of bulk graphite. The thermal conductivity of graphene on SiO<sub>2</sub> is still high but lower compared to suspended graphene due to interface interactions. GNRs as well as the Mo- and W-based TMDs show lower thermal conductivities.

Table 5 shows the thermal boundary resistance  $R_{TB}$  of graphene/SiO2, graphene/SiC, and graphene/BN junctions and for comparison that of silicon on SiO2 as used in modern SOI structures. Unfortunately, information on the thermal boundary resistance for the 2D materials beyond graphene is not yet

**Table 4** Room temperature thermal conductivity  $\kappa$  of 3D bulk and single-layer 2D materials (unit W m<sup>-1</sup> K<sup>-1</sup>), e: Experiment: s: simulated

Feature article

| 3D bulk materials |      | 2D materials |                   |                  |        |      |

|-------------------|------|--------------|-------------------|------------------|--------|------|

|                   | κ    | Ref.         | -                 | Substrate        | κ      | Ref. |

| Si                | 130  | 44           | Graphene          | SiO <sub>2</sub> | e, 600 | 141  |

| SiC               | 290  | 44           | GNR               | $SiO_2$          | e, 80  | 142  |

| $SiO_2$           | 1.5  | 44           | $MoS_2$           | No substrate     | e, 34  | 143  |

| Graphite          | 2000 | 139          | $MoS_2$           | No substrate     | s, 103 | 144  |

| $MoS_2$           | 2.4  | 140          | MoSe <sub>2</sub> | No substrate     | s, 54  | 144  |

| $WS_2$            | 1.9  | 140          | $WS_2$            | No substrate     | s, 142 | 144  |

| $WSe_2$           | 1.2  | 140          | $WSe_2$           | No substrate     | s, 53  | 144  |

**Table 5** Thermal boundary resistance of graphene and Si on different substrates in units of  $10^{-8}$  m<sup>2</sup> K W<sup>-1</sup>. xL: x layers; e: experiment; s: simulated

| Channel                                            | Underlying<br>material  | $R_{\mathrm{TB}}$                                                                                   | Remarks                                                                                                        | Ref.                                                   |

|----------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Graphene<br>Graphene<br>Graphene<br>Graphene<br>Si | SiO <sub>2</sub><br>SiC | $0.5^{\dagger} \le 2.0^{\#} \le 4^{\$}$ $0.56^{\dagger}, 1.2^{\#}$ $3.6$ $0.535$ $0.05-0.15$ $0.23$ | e, 5L <sup>†</sup> , average <sup>#</sup> , SL <sup>§</sup> e, 2L <sup>†</sup> , SL <sup>#</sup> s, 3L s, 8L s | 145<br>146<br>149<br>149<br>147, 148<br>and 150<br>151 |

available. The measured  $R_{TB}$  of single-layer graphene on SiO<sub>2</sub> 145,146 is more than a factor of 10 larger than that calculated for Si on SiO2. 147,148 This factor of 10, however, is less critical than it seems on first sight. Usually the thermal resistance encountered by the heat flow from the chip surface (where the devices are located and the heat is generated) to the heat sink at the back side of the chip is much larger than the thermal boundary resistance the heat has to surmount when flowing from the 2D channel to the underlying substrate. To illustrate this issue, let us consider a graphene device layer located on a Si wafer (thickness  $t_{Si} = 360 \mu m$ ) covered with SiO<sub>2</sub> (thickness  $t_{SiO_2}$  = 90 nm) and assume the simplified case of a homogeneous heat flow from the graphene layer downward to the bottom of the substrate. The heat generated in the graphene layer first crosses the graphene/SiO<sub>2</sub> interface having a thermal boundary resistance  $R_{TB1}$ , flows through the SiO<sub>2</sub> layer with a thermal resistance  $R_{\text{th-ox}}$ , then crosses the SiO<sub>2</sub>/Si interface  $(R_{TB2})$ , and finally flows through the Si substrate  $(R_{th-Si})$ .

The overall thermal resistance is the sum of the individual contributions  $^{152}$  and reads as

$$R_{\text{th}} = (R_{\text{TB1}} + R_{\text{th-ox}} + R_{\text{TB2}} + R_{\text{th-Si}}) \times \frac{1}{A}$$

$$= \left(R_{\text{TB1}} + \frac{t_{\text{SiO}_2}}{\kappa_{\text{SiO}_2}} + R_{\text{TB2}} + \frac{t_{\text{Si}}}{\kappa_{\text{Si}}} R_{\text{th-Si}}\right) \times \frac{1}{A}$$

(11)

where *A* is the area of the device layer. Using the data from Tables 4 and 5, one obtains  $R_{\rm TB1} = 10^{-8} \ {\rm m^2 \ K \ W^{-1}}$ ,  $R_{\rm th-ox} = 6 \times 10^{-8} \ {\rm m^2 \ K \ W^{-1}}$ ,  $R_{\rm TB2} = 10^{-9} \ {\rm m^2 \ K \ W^{-1}}$ , and  $R_{\rm th-Si} = 2.8 \times 10^{-6}$

m<sup>2</sup> K W<sup>-1</sup>, which clearly shows the dominating role of the substrate for heat removal.

Note that the heat transport parameters from Tables 4 and 5 relate to room temperature. When the temperature rises beyond room temperature, the thermal conductance decreases (undesirable) and the thermal boundary resistance decreases (desirable) as well. 149,153

Reliable targets for the thermal conductivity and the thermal boundary resistance of FET channel materials have not yet been established. It is certainly fair, however, to state that both  $\kappa$  and  $R_{\rm TB}$  of the 2D materials should not fall far behind those of Si and the III–V compounds.

### 4.5 Contact resistance

The first contact experiments for 2D materials have been focused on graphene and revealed that achieving low-resistance contacts is challenging. In late 2010, the best metal–graphene contact resistances have been in the range 0.5–10  $\Omega$  mm, <sup>154</sup> *i.e.*, orders of magnitude higher than for contacts to Si and III–V compounds. Therefore, a lot of effort has been invested in reducing the metal–graphene contact resistance that finally led to significant improvements. Today, metal–graphene contact resistances as low as 0.01–0.2  $\Omega$  mm have been achieved. This already comes close to the resistance of state-of-the-art metal contacts on Si and III–V semiconductors.

Meanwhile, data for metal–TMD and metal–phosphorene contacts have been reported as well. Here, however, the contact resistance is still too high and typically exceeds 0.5  $\Omega$  mm. Table 6 summarizes the state-of-the-art metal contacts on 2D materials and on conventional semiconductors.

From the ITRS one can get an impression about the contact requirements related to logic MOSFETs. During the entire horizon of the 2013 ITRS edition, the maximum allowed parasitic resistance (which includes both the contact resistance itself and the semiconductor series resistance, see eqn (4)) is around 0.065  $\Omega$  mm. Thus, the contact resistance must be significantly below 0.065  $\Omega$  mm. As Table 6 indicates, so far only

**Table 6** Contact resistance of different FET structures. SL: single layer; BL: bilayer; FL: few-layer

| Transistor<br>type      | $R_{\rm co} \ (\Omega \ { m mm})$ | Metal                   | Comment             | Ref.           |

|-------------------------|-----------------------------------|-------------------------|---------------------|----------------|

| Graphene<br>MOSFET      | 0.011-0.08                        | Ni, Ti                  | BL                  | 155 and<br>156 |

|                         | 0.1-0.2                           | Ti, Ni, Pd/Au,<br>Cr/Au | SL                  | 155-158        |

| MoS <sub>2</sub> MOSFET | 0.2-1.6                           | Ni/Au, Ti/Au,<br>Au     | FL                  | 159-162        |

|                         | 2                                 | Au                      | $\operatorname{SL}$ | 163            |

| WSe <sub>2</sub> MOSFET | 1.4                               | Graphene                | BL                  | 164            |

|                         | 2                                 | Graphene                | FL                  | 165            |

| Phosphorene<br>MOSFET   | 1.75                              | Ni/Au, PdAu             | FL                  | 166            |

| Si MOSFET               | < 0.01                            |                         |                     | 167            |

| InP HEMT                | 0.03                              |                         |                     | 168            |

| GaAs mHEMT              | 0.02                              |                         |                     | 169            |

**Table 7** Scale lengths of 2D MOSFETs and competing conventional FET types, all with one single top-gate

| Transistor class        | $arepsilon_{	ext{r-ch}}$ | $\varepsilon_{	ext{r-bar}}$ | $t_{ m ch} \  m (nm)$ | $t_{ m bar} \  m (nm)$ | λ<br>(nm) |

|-------------------------|--------------------------|-----------------------------|-----------------------|------------------------|-----------|

| Si SOI MOSFET           | 11.9                     | 3.9                         | 5                     | 0.6                    | 3         |

| InP HEMT & GaAs mHEMT   | 14.1                     | 12.7                        | 15                    | 15                     | 16        |

| GNR MOSFET              | 1.8                      | 3.9                         | 0.35                  | 0.6                    | <1        |

| MoS <sub>2</sub> MOSFET | 2.8                      | 3.9                         | 0.72                  | 0.6                    | <1        |

graphene has fulfilled this requirement. Given the successful reduction of  $R_{\rm co}$  for metal–graphene contacts by more than an order of magnitude within a few years, we expect sizeable improvements for TMD and phosphorene contacts in the near future as well.

### 4.6 Scale length

Nanoscale

Table 7 shows the scale length  $\lambda$  of GNR, MoS<sub>2</sub>, and Si MOSFETs as well as of InP HEMTs and GaAs mHEMTs obtained using eqn (8). The results indicate that, in terms of scale length and thus regarding the suppression of short-channel effects and scaling limits, the FETs with 2D channels behave much better than those with conventional channel materials.

## State-of-the-art 2D FETs

In the following, the status of research on 2D transistors is reviewed by presenting experimental transistor data collected from the literature. In addition, transistor performance trends are discussed on the basis of theoretical considerations.

### 5.1 X-ene FETs

**5.1.1 Graphene FETs.** Recently, several comprehensive review papers on the state-of-the-art graphene FETs have been published. Therefore, we only summarize the main messages of these papers and refer the reader to ref. 3, 102, 170 and 171 for more details.

5.1.2 Graphene MOSFETs for digital logic. MOSFETs with gapless large-area graphene channels do not switch off and show on-off ratios of only 2–10. Thus, large-area graphene is not a suitable channel material for logic MOSFETs. Back-gate GNR MOSFETs with on-off ratios of 10<sup>4</sup> to >10<sup>6</sup> have been successfully fabricated. <sup>91,172,173</sup> Due to the thick back-gate dielectrics, however, these transistors need unacceptably large gate voltage swings of 3–20 V for switching. As we have shown in Fig. 2, the supply voltage for logic circuits (and thus the maximum available gate voltage swing) is currently below 1 V and is required to decrease further in the future. Therefore, top-gate GNR MOSFETs with very thin gate dielectrics are needed to achieve good switching behavior with a sub-1 V gate voltage swing. Moreover, as has been shown in Fig. 11, the gap opening in GNRs is accompanied by a dramatic mobility

reduction. For these reasons, in the short to medium term the application of GNR MOSFETs in digital logic is rather unlikely. Things may change at 5 nm and below gate length levels when direct source–drain tunneling becomes an issue.

To circumvent the problems of gapless large-area graphene, vertical non-FET transistor concepts that do not require a gap for switch-off have been elaborated. These concepts rely either on graphene–Si Schottky barriers as described in ref. 174, where on–off ratios of up to 10<sup>5</sup> have been demonstrated, on tunneling through an insulator between two graphene layers, <sup>175</sup> or on using graphene as the base of a hot electron transistor. These devices represent interesting options to exploit gapless graphene in logic transistors and can in general be realized also using 2D materials beyond graphene. It is difficult, however, to assess their true potential for future logic at the moment.

5.1.3 Graphene MOSFETs for RF. So far, only experimental graphene RF FETs with gapless channels have been reported. Soon after the demonstration of the first graphene MOSFET with a gapless channel, <sup>177</sup> the RF capabilities of such transistors have been investigated, <sup>178</sup> and meanwhile many groups have realized RF MOSFETs with gapless graphene channels. Table 8 summarizes the best reported cutoff frequencies  $f_{\rm T}$  and maximum frequencies  $f_{\rm max}$  of such graphene MOSFETs, together with the  $f_{\rm T}-f_{\rm max}$  performance of competing RF FET types. More details can be found in the  $f_{\rm T}$  vs. L and  $f_{\rm max}$  vs. L plots of ref. 3.

In terms of  $f_{\rm T}$ , graphene MOSFETs perform competitively. They outperform Si MOSFETs with comparable size and compete well with InP HEMTs and GaAs mHEMTs (which are the fastest RF FETs of all) down to gate lengths of about 60 nm.<sup>3</sup> Regarding the more important FOM  $f_{\rm max}$ , however, the picture looks less promising for graphene MOSFETs. While the record  $f_{\rm max}$  of InP HEMTs and GaAs mHEMTs exceeds 1 THz and Si MOSFETs with an  $f_{\rm max}$  of 420 GHz have been reported, the best graphene RF FETs show an  $f_{\rm max}$  of about 100 GHz only.<sup>182</sup> It has been discussed in detail that the main reason for this poor  $f_{\rm max}$  performance is the missing gap in large-area graphene.<sup>3</sup> Thus, no matter how carefully the design of large-area graphene FETs is optimized, these transistors will

**Table 8** The best  $f_T$  and  $f_{max}$  data for graphene RF MOSFETs with gapless channels and for competing RF FETs. L is the gate length

| FET type          | L (nm) | $f_{\mathrm{T}}\left(\mathrm{GHz}\right)$ | $f_{\rm max}\left({ m GHz}\right)$ | Ref. |

|-------------------|--------|-------------------------------------------|------------------------------------|------|

| Graphene MOSFET   | 67     | 427                                       | _                                  | 179  |

| (gapless channel) | 40     | 350                                       | 22                                 | 180  |

| (8-1 )            | 144    | 300                                       | _                                  | 181  |

|                   | 100    | 93                                        | 105                                | 182  |

| InP HEMT          | 30     | 644                                       | 681                                | 183  |

|                   | 30     | 600                                       | 1200                               | 36   |

| GaAs mHEMT        | 40     | 688                                       | 800                                | 75   |

|                   | 35     | 515                                       | >1000                              | 76   |

| Si MOSFET         | 29     | 485                                       | _                                  | 184  |

|                   | 29     | 360                                       | 420                                | 185  |

|                   | 28     | 395                                       | 410                                | 186  |

**Table 9**  $f_{\rm T}$  and  $f_{\rm max}$  of 260 nm gate graphene MOSFETs obtained by different de-embedding procedures<sup>187</sup>

|                                                                                       | As measured | Pad de-embedding | Full de-embedding |

|---------------------------------------------------------------------------------------|-------------|------------------|-------------------|

| $f_{\mathrm{T}}\left(\mathrm{GHz}\right)$ $f_{\mathrm{max}}\left(\mathrm{GHz}\right)$ | 23.6        | 38.7             | 198               |